## DESIGN OF SINGLE-INDUCTOR MULTIPLE-OUTPUT CONVERTER FOR LOW POWER & HIGH EFFICIENCY APPLICATIONS

### By

Luis A. Malavé Pérez

A thesis submitted in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

in

## ELECTRICAL ENGINEERING UNIVERSITY OF PUERTO RICO MAYAGÜEZ CAMPUS May 2015

Approved by:

Guillermo Serrano, Ph.D.<br/>Chairman, Graduate CommitteeDateEduardo Ortiz, Ph.D.<br/>Member, Graduate CommitteeDateRogelio Palomera, Ph.D.<br/>Member, Graduate CommitteeDateMauricio Cabrera, Ph.D.<br/>Graduate Studies RepresentativeDateRaúl Torres, Ph.D.<br/>Department ChairpersonDate

Abstract of Thesis Presented to the Graduate School of the University of Puerto Rico in Partial Fulfillment of the Requirements for the Degree of Master of Science

## DESIGN OF SINGLE-INDUCTOR MULTIPLE-OUTPUT CONVERTER FOR LOW POWER & HIGH EFFICIENCY APPLICATIONS

By

Luis A. Malavé Pérez

May 2015

Chair: Dr. Guillermo Serrano Department: Electrical and Computer Engineering Department

This work presents a control architecture for Single Inductor Multiple Output (SIMO) converters applied to low power applications. A functional Power Management Integrated Circuit (PMIC) was designed, simulated, and fabricated, using a  $0.8\mu$ m BiCMOS technology, to provide three totally independent output voltages by using only one external inductor. The proposed hybrid operation mode, along with the stable non-invasive inductor current controller, allows the system to achieve high efficiencies even under low load conditions. The system's architecture exhibits maximum efficiency of 85% with nominal loads of  $25\mu$ A,  $25\mu$ A, and  $10\mu$ A; with less than  $1\mu$ A of controller current consumption.

Resumen de Tesis Presentado a Escuela Graduada de la Universidad de Puerto Rico como requisito parcial de los Requerimientos para el grado de Maestría en Ciencias

## DISEÑO DE CONVERTIDOR SINGLE-INDUCTOR MULTIPLE-OUTPUT PARA APLICACIONES DE BAJA POTENCIA Y ALTA EFICIENCIA

Por

Luis A. Malavé Pérez

Mayo 2015

Consejero: Dr. Guillermo Serrano Departamento: Ingeniería Eléctrica y de Computadoras

Este trabajo presenta una arquitectura de control para convertidores "Single Inductor Multiple Output" (SIMO) aplicada a aplicaciones de baja potencia. Se diseñó, simuló, y probó experimentalmente un Circuito Integrado de Manejo de Potencia (PMIC por sus siglas en inglés) usando una tecnología BiCMOS de 0.8µm, para proveer tres voltajes de salida totalmente independientes mediante el uso de un solo inductor externo. Bajo condiciones nominales, se alcanzó una eficiencia de 85% mediante la implementación de un controlador que consume menos de 1µA durante su estado inactivo. El modo híbrido de operación, junto con el controlador estable de corriente de inductor, permite al sistema alcanzar altas eficiencias aún bajo condiciones de baja potencia.

To my father, my mother, my brother, and my fiancée Rosedanny who always makes me feel loved.

## Acknowledgments

First, I'll like to thank God for being by my side all this time; and for loving me unconditionally. Second, I'll like to acknowledge all the people who have supported me during this adventure. Thanks to my parents and brother for always being there for me. And to my fiancée Rosedanny, who loved me from the beginning, and supported me during this time.

Likewise, I'll like to thanks my advisor Dr. Guillermo Serrano for guiding me wisely during all this time. Also, thanks to Charles Parkhurst who accepted to be my mentor from Texas Instruments. This work wouldn't have been a reality without the mentoring and motivation of these two persons. In addition, thanks to Dr. Eduardo Ortiz, Dr. Andrés Díaz, and Dr. Rogelio Palomera for accepting to be part of this initiative. And thanks to my counselor Mrs. Sandra Montalvo for guiding me during this race. Special thanks to all my colleagues in the Power Electronics (S-101), Integrated Circuit Design Laboratory (ICDL) and Electronic Testing and Characterization (ETC) laboratories who always supported me.

Finally, but not less important, to all my friends who contributed a sand grain to be who I am today. Thanks to all the people that directly or indirectly contributed to this experience. Blessings for everyone!

# Table of Contents

| Abstract  | in English                                    | ii   |

|-----------|-----------------------------------------------|------|

| Abstract  | in Spanish                                    | iii  |

| Acknowle  | edgments                                      | v    |

| Table of  | Contents                                      | vi   |

| Equation  | s List                                        | viii |

| Tables Li | st                                            | ix   |

| Figures L | ist                                           | x    |

| Chapter : | 1 : Introduction                              | 1    |

| 1.1       | Objectives                                    | 2    |

| 1.2       | Content Organization                          | 3    |

| Chapter 2 | 2 : Previous Works & Architecture Selection   | 4    |

| 2.1       | Literature Review & Topologies Overview       | 5    |

| 2.2       | Proposed Architecture                         | 12   |

| Chapter 3 | 3 : System's Design & Components Overview     |      |

| 3.1       | System's Components Overview                  | 19   |

| 3.2       | Reference System (Refsys)                     | 21   |

| 3.3       | Inductor Peak Current Sensor (IPK)            |      |

| 3.4       | Zero Current Detector (ZCD)                   | 44   |

| 3.5       | Logic                                         | 50   |

| 3.6       | Charge Monitor (CharMon)                      | 57   |

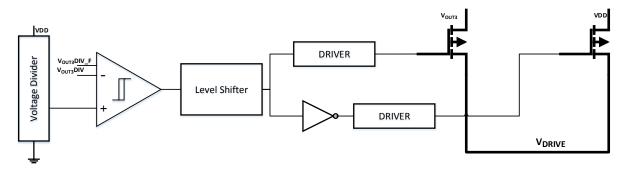

| 3.7       | V <sub>DRIVE</sub> Selector                   | 66   |

| 3.8       | Level Shifters (LS)                           | 70   |

| 3.9       | Drivers (DRIVERS)                             | 72   |

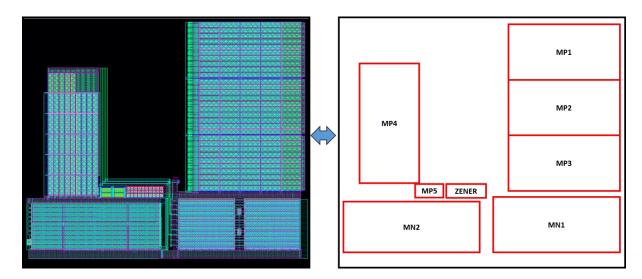

| 3.10      | Switches                                      | 75   |

| Chapter 4 | 4 : System Simulations & Experimental Results | 81   |

| 4.1       | Experimental Overview                         | 82   |

| 4.2       | Switching Cycle                               | 84   |

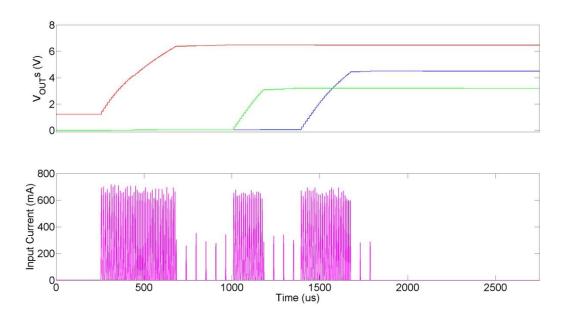

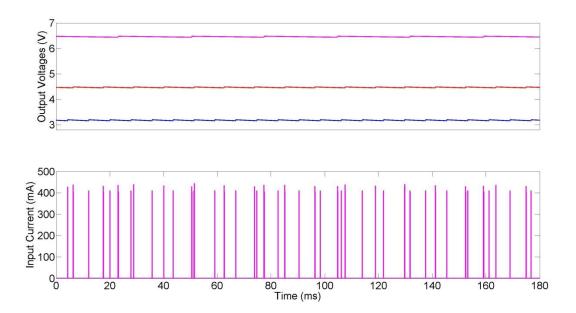

| 4.3       | System's Startup                              | 87   |

| 4.4       | Output Regulation                             | 89   |

| 4.5       | System's Efficiency and Results Overview      | 93   |

| Chapter ! | 5 : Conclusions & Future Work                 | 97   |

| Referenc  | es                                            |      |

| Appendix A – Cellviews and Layouts | 101 |

|------------------------------------|-----|

| Appendix B – Testing Setup         | 111 |

# **Equations List**

| Equation (1) Dickson Charge Pump Efficiency                                       | 6    |

|-----------------------------------------------------------------------------------|------|

| Equation (2) Criterion for DCM                                                    | 7    |

| Equation (3) I <sub>MP7</sub> Current Equation                                    | . 22 |

| Equation (4) Internal Reference Voltage Equation                                  | . 22 |

| Equation (5) Internal Reference Temperature Derivative                            | .22  |

| Equation (6) Design Equation for TC Cancellation                                  | . 22 |

| Equation (7) I <sub>MP4</sub> CTAT Current                                        | . 25 |

| Equation (8) IREF Temperature Coefficient Equation                                | .26  |

| Equation (9) I <sub>CTAT</sub> Resistor Value Equation                            | .26  |

| Equation (10) Power and Sense Transistor Currents Rate Equations                  | .36  |

| Equation (11) Inductor Peak Current Value                                         | .36  |

| Equation (12) Parasitic Voltage Drop of V <sub>DRAIN_A</sub>                      | .41  |

| Equation (13) Inductor Peak Current Value, including Parasitic Resistances Effect | .41  |

| Equation (14) K <sub>ERROR</sub> Formula                                          | .41  |

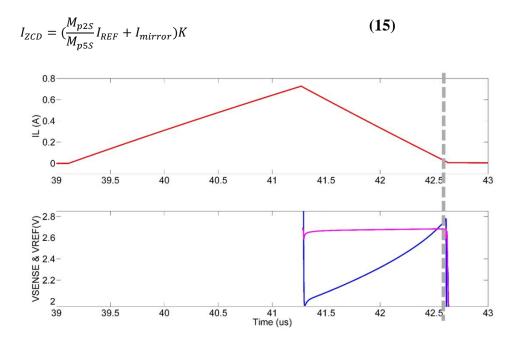

| Equation (15) Inductor Zero Current Value                                         | .45  |

| Equation (16) ZCD value including Parasitic Resistances Effect                    | .47  |

| Equation (17) K <sub>ERROR</sub> Formula for ZCD                                  | .47  |

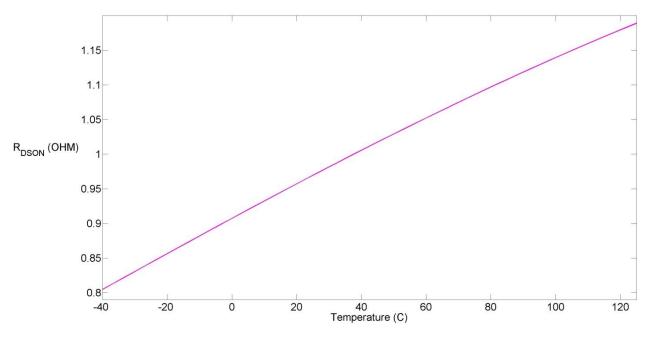

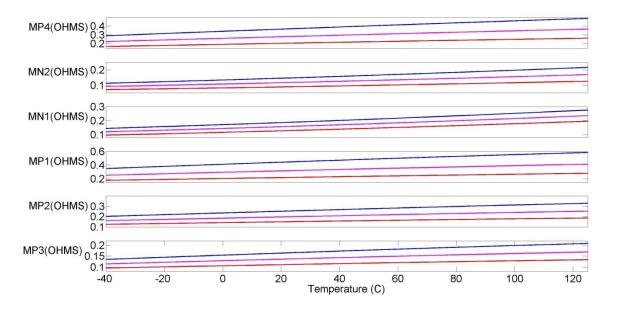

| Equation (18) Switches' MP4 Internal Resistance Maximum                           | .76  |

# **Tables List**

| Table 1 Switching Converters Gain Equations           | 8  |

|-------------------------------------------------------|----|

| Table 2 SIMO Converter Efficiency Equations           | 10 |

| Table 3 Module Design Specifications                  | 20 |

| Table 4 IPK Simulation Data                           | 41 |

| Table 5 ZCD Simulation Data                           | 47 |

| Table 6 Switches Module Power Transistors Size        | 77 |

| Table 7 Simulation and Experimental Tests Description | 83 |

| Table 8 System's Performance Summary                  | 96 |

# Figures List

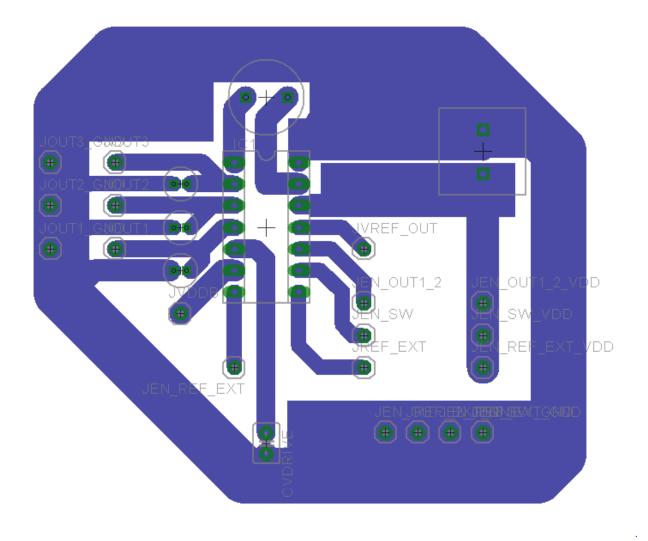

| Figure 1-1 Application Block Diagram                                                      | 2  |

|-------------------------------------------------------------------------------------------|----|

| Figure 2-1 Dickson Charge Pump                                                            | 6  |

| Figure 2-2 Buck Converter                                                                 | 7  |

| Figure 2-3 Boost Converter                                                                | 7  |

| Figure 2-4 SIMO Buck-Boost Converter                                                      | 9  |

| Figure 2-5 SIMO Converter Efficiency Equations Plot                                       | 11 |

| Figure 2-6 SIMO Distributive Mode Time Diagram                                            |    |

| Figure 2-7 SIMO Sequential Mode Time Diagram                                              | 14 |

| Figure 2-8 Hybrid Mode Time Diagram                                                       | 15 |

| Figure 2-9 State Machine's State Diagram                                                  | 16 |

| Figure 2-10 SIMO Converter Topology and Controller                                        | 17 |

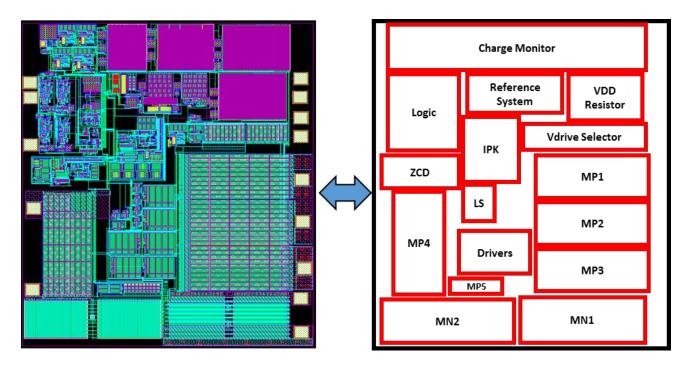

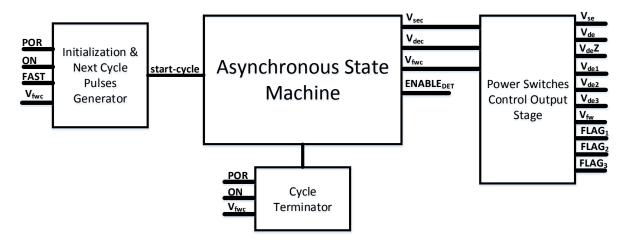

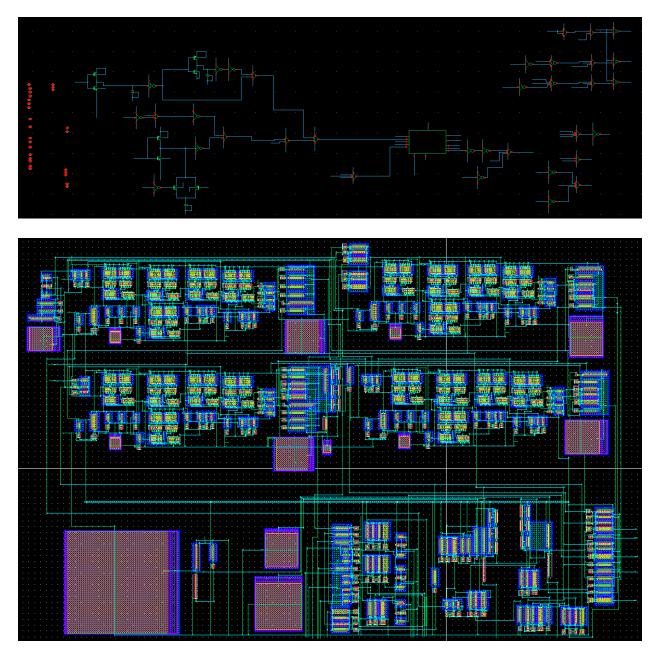

| Figure 3-1 Device's Map of Modules                                                        | 19 |

| Figure 3-2 Internal Reference Voltage Schematic                                           | 21 |

| Figure 3-3 Reference Voltage Temperature-DC Sweep                                         | 24 |

| Figure 3-4 Current Reference Generator Schematic                                          | 25 |

| Figure 3-5 Reference Current Temperature-DC Sweep                                         | 26 |

| Figure 3-6 Supply Current Temperature-DC Sweep                                            | 27 |

| Figure 3-7 Reference System's Layout                                                      | 28 |

| Figure 3-8 R3 and R4 Resistors Matching Distribution for Internal Reference Voltage       | 29 |

| Figure 3-9 BJT Transistors Q1 & Q2 Distribution for Internal Reference Voltage            | 30 |

| Figure 3-10 Inductor Peak Current Sensor Block Diagram                                    | 32 |

| Figure 3-11 Delay Circuit Low-to-High Edge                                                | 33 |

| Figure 3-12 Delay Circuit Example Plot                                                    | 33 |

| Figure 3-13 IPK Starter Component Schematic                                               | 34 |

| Figure 3-14 IPK Current Reference Amplifier                                               | 35 |

| Figure 3-15 IPK Current Sensor Topology Diagram                                           | 37 |

| Figure 3-16 Inductor Peak Current Control, VSENSE & VREF                                  | 38 |

| Figure 3-17 Inductor Peak Current Sensor's Hysteretic Comparator                          | 39 |

| Figure 3-18 Hysteretic Comparator Operation Plot                                          | 39 |

| Figure 3-19 IPK Module Performance Plot                                                   | 40 |

| Figure 3-20 Inductor Peak Current Sensor's Layout                                         | 43 |

| Figure 3-21 IPK Current-Voltage Converter & Reference Voltage Generator Matching          | 43 |

| Figure 3-22 Inductor ZCD Current Control, VSENSE & VREF                                   | 45 |

| Figure 3-23 ZCD Topology Diagram                                                          | 46 |

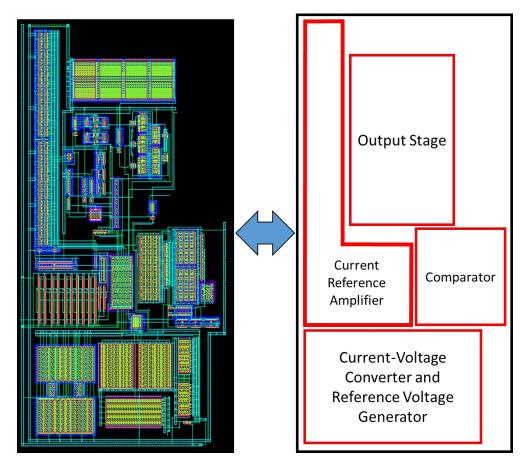

| Figure 3-24 ZCD Sensor's Layout                                                           | 49 |

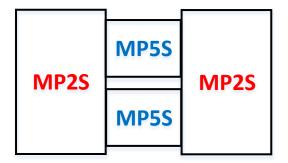

| Figure 3-25 IPK Current-Voltage Converter & Reference Voltage Generator PMOS Distribution | 49 |

| Figure 3-26 Logic Module's Block Diagram                                                  | 50 |

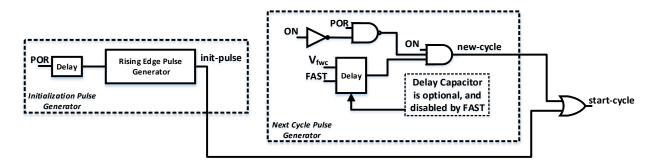

| Figure 3-27 Initialization & Next Cycle Pulses Generator Schematic                        | 51 |

| Figure 3-28 Rising Edge Pulse Generator Schematic                                         | 52 |

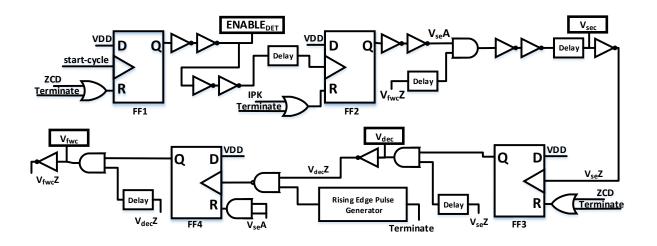

| Figure 3-29 Logic Module's Asynchronous State Machine                                     | 53 |

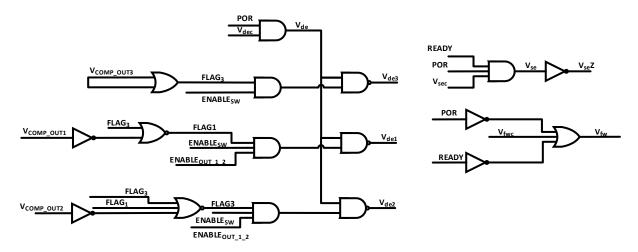

| Figure 3-30 Logic Module's Power Switches Control Output                                  | 54 |

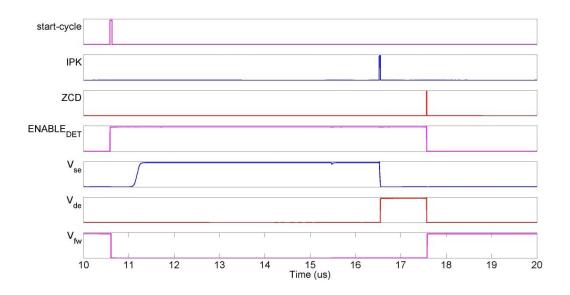

| Figure 3-31 Logic Module's State Machine Performance                                      |    |

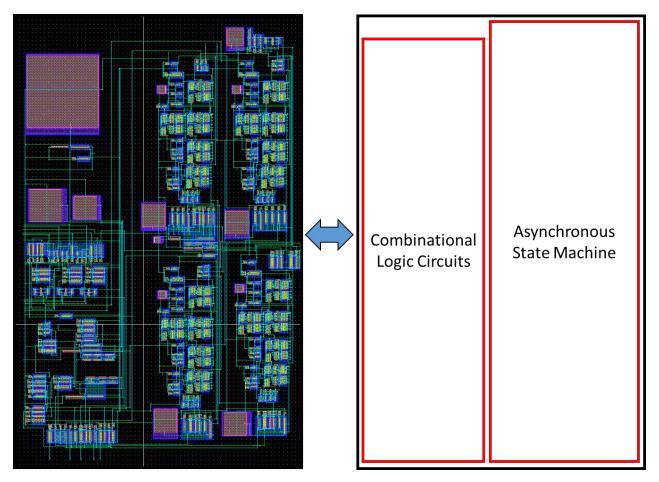

| Figure 3-32 Logic Module's Layout                                    |    |

|----------------------------------------------------------------------|----|

| Figure 3-33 Charge Monitor Block Diagram                             |    |

| Figure 3-34 Voltage Divider Circuit                                  |    |

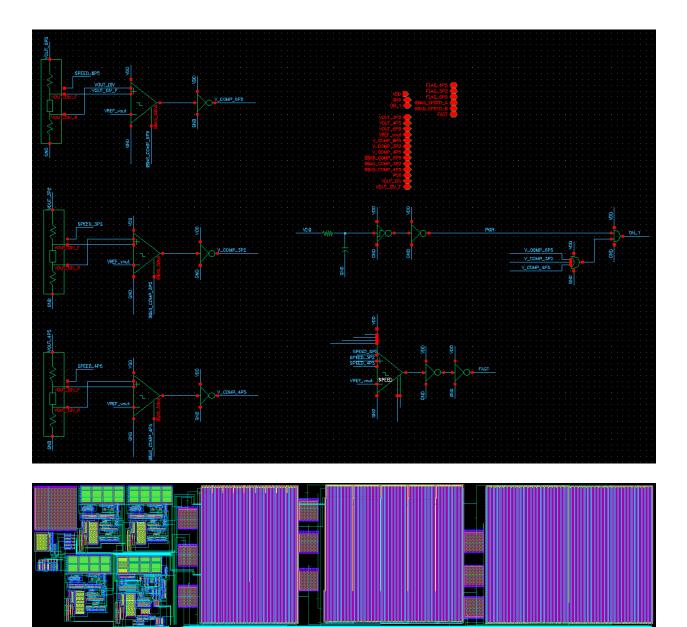

| Figure 3-35 Charge Monitor Output Monitoring Comparators             |    |

| Figure 3-36 Charge Monitor SPEED Comparator                          | 61 |

| Figure 3-37 Charge Monitor Output Comparators Performance Plot       | 62 |

| Figure 3-38 Charge Monitor SPEED Comparator Performance Plot         | 63 |

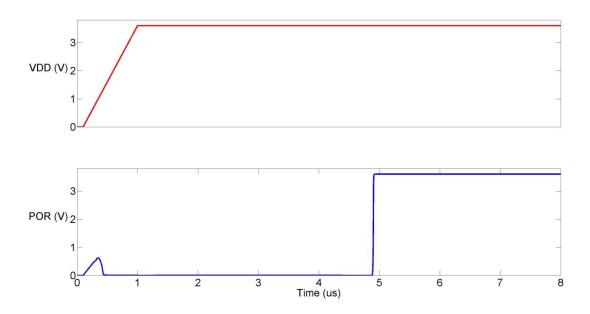

| Figure 3-39 Charge Monitor POR Performance                           | 63 |

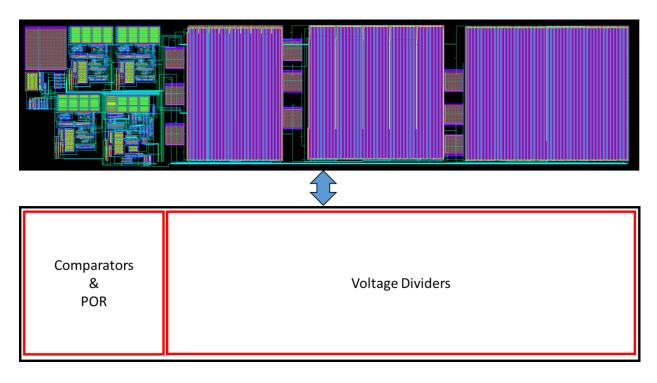

| Figure 3-40 Charge Monitor Layout Map                                | 64 |

| Figure 3-41 Charge Module V <sub>OUT2</sub> Resistor Divider         | 65 |

| Figure 3-42 Charge Module V <sub>OUT1</sub> Resistor Divider         | 65 |

| Figure 3-43 VDRIVE Selector Schematic                                | 67 |

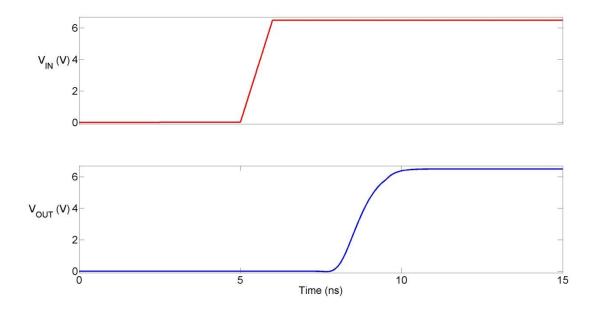

| Figure 3-44 VDRIVE Selector Performance Transient                    |    |

| Figure 3-45 VDRIVE Selector Switches Resistance                      |    |

| Figure 3-46 VDRIVE Selector Layout Map                               |    |

| Figure 3-47 Level Shifter Schematic                                  | 70 |

| Figure 3-48 Level Shifter Performance Plot                           | 71 |

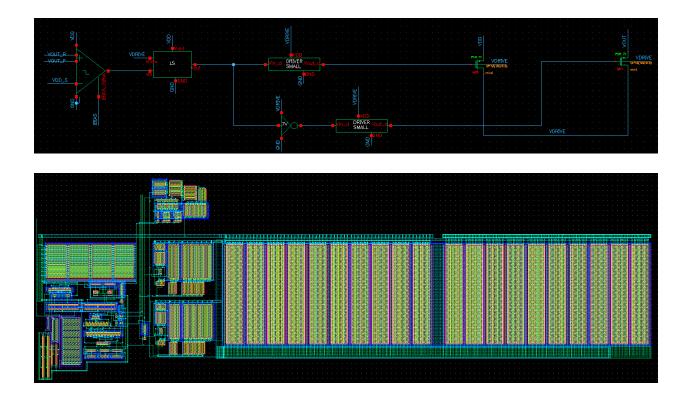

| Figure 3-49 Driver Module Schematic                                  | 72 |

| Figure 3-50 Driver Performance Plot                                  | 73 |

| Figure 3-51 Driver Module's Layout                                   |    |

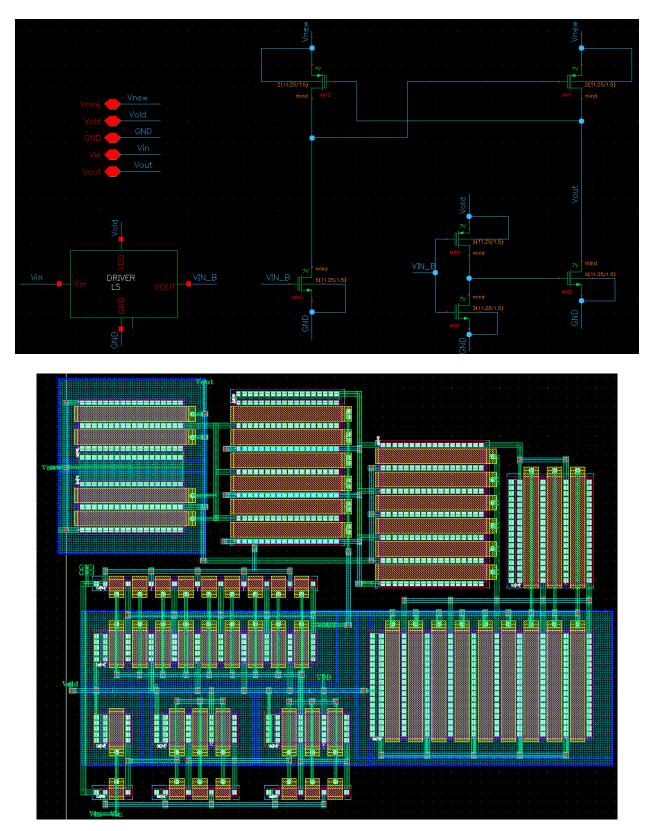

| Figure 3-52 Switches Module's Schematic                              | 75 |

| Figure 3-53 Switches Energization Stage                              | 76 |

| Figure 3-54 Switches Internal Resistance Plot                        | 77 |

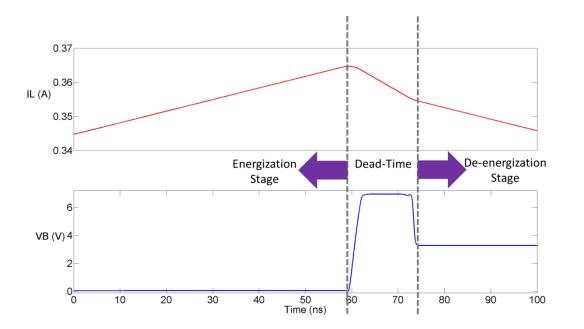

| Figure 3-55 Dead Time & V <sub>B</sub> Node Voltage Raise Protection |    |

| Figure 3-56 Switches Module Layout                                   | 79 |

| Figure 3-57 Sensing Transistors Layout Distribution Map              |    |

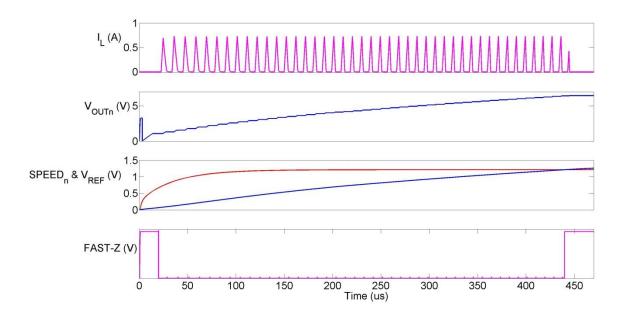

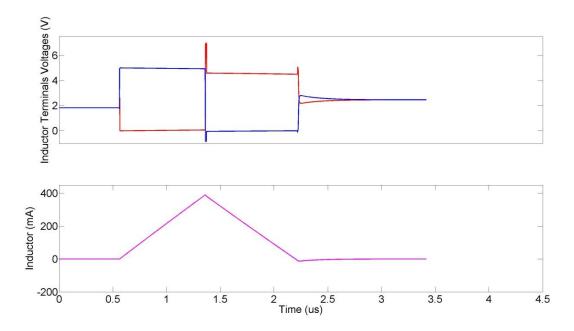

| Figure 4-1 Switching Cycle Inductor Current Simulation Data          |    |

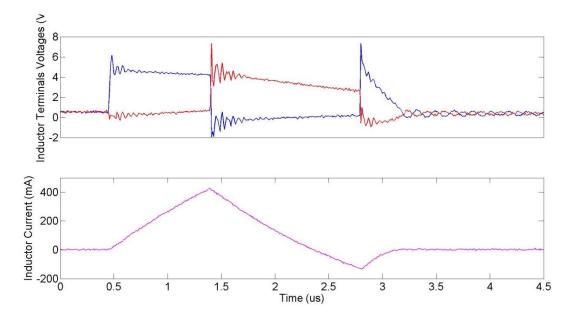

| Figure 4-2 Switching Cycle Inductor Current Experimental Data        |    |

| Figure 4-3 Switching Cycle Dual De-Energization Experimental Data    |    |

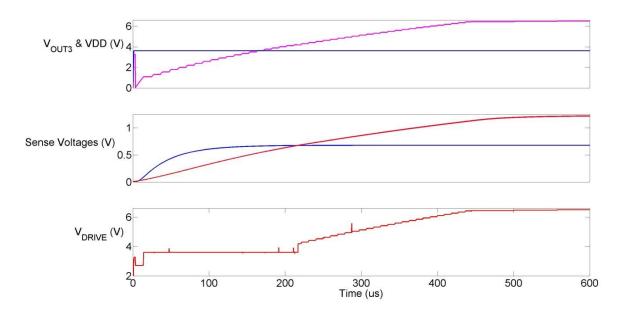

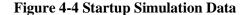

| Figure 4-4 Startup Simulation Data                                   |    |

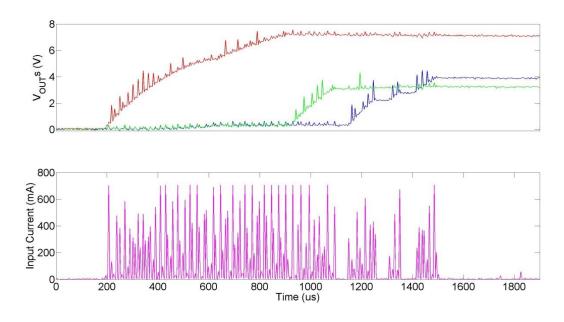

| Figure 4-5 Startup Experimental Data                                 |    |

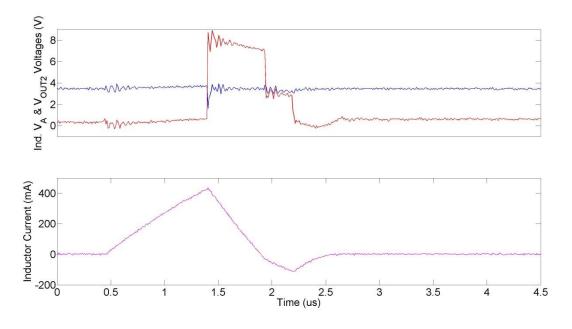

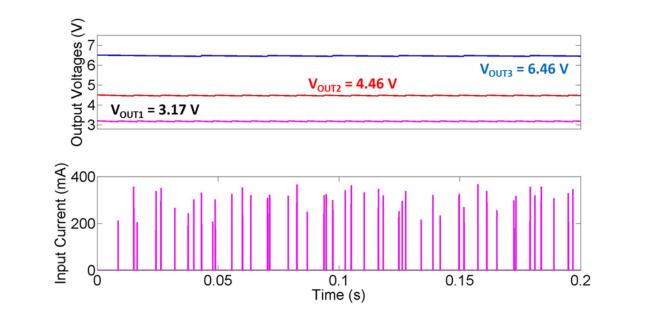

| Figure 4-6 Nominal Load Regulation Simulation Data                   |    |

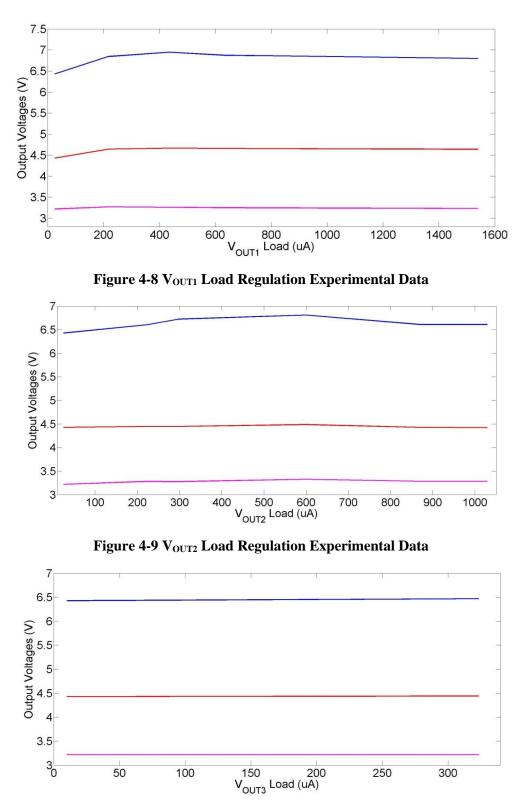

| Figure 4-7 Nominal Load Regulation Experimental Data                 | 90 |

| Figure 4-8 V <sub>OUT1</sub> Load Regulation Experimental Data       | 91 |

| Figure 4-9 V <sub>OUT2</sub> Load Regulation Experimental Data       | 91 |

| Figure 4-10 V <sub>OUT3</sub> Load Regulation Experimental Data      | 91 |

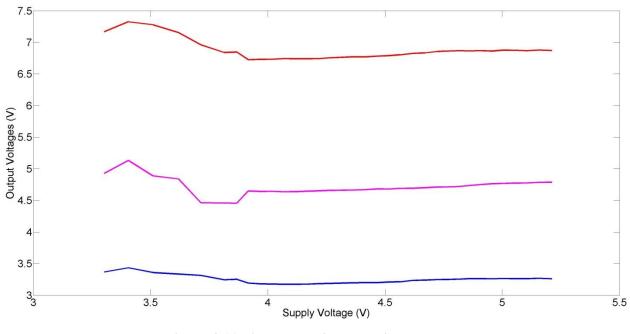

| Figure 4-11 Line Regulation Experimental Data                        |    |

| Figure 4-12 Efficiency Calculation Simulation Data                   | 93 |

## Chapter 1 : Introduction

All electronic devices are powered from a source of energy, typically in the form of batteries. The unregulated power obtained from batteries requires proper regulation through the use of power management integrated circuits (PMICs). PMICs play an essential role on the device life as its efficiency will have a direct effect on the energy delivered to the device. Additionally, the use of external component is a key design parameter, particularly in portable and wearable applications where the device area reduction is one of the design priorities. The quantity and size of the external components will affect the production cost of the integrated circuit (IC) along with its size [1].

This research presents the design, simulation, and experimental validation of a PMIC for wearable devices applications. Design techniques like dynamic powering, low quiescent current, and non-invasive current sensing are used to implement a Single-Inductor Multiple-Output (SIMO) DC-DC converter that works in a proposed Sequential-Distributive hybrid operation mode. The implementation of an 85% efficient PMIC which minimizes the use of external components is discussed in detail, which is one of the main contributions of this research to the field of low power DC-DC converters.

## 1.1 Objectives

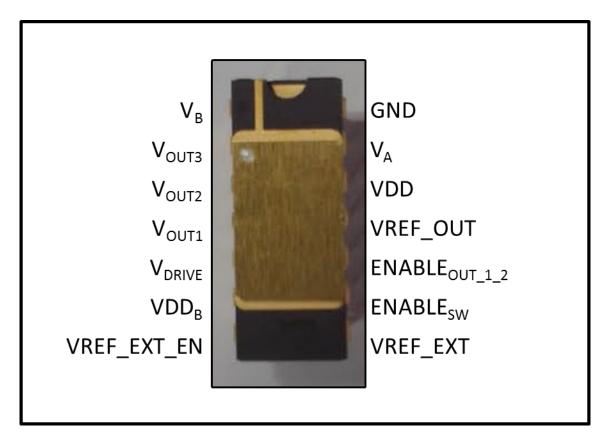

Figure 1-1 shows a block diagram of the power management system of a typical digital wrist watch. The PMIC module, labeled as "Display PMIC", supplies three different and independent output voltages to a digital display. A lithium battery provides the unregulated power to the PMIC. This work presents the design, simulation and experimental evaluation of a PMIC with the following specifications:

- Three independent and regulated output voltages.

- 3.2 V @ 25µA of nominal load

- 4.5 V @ 25µA of nominal load

- 6.5 V @ 10µA of nominal load

- An input voltage range of (2.5 5.5) V

- A 85% efficiency at nominal load

- Minimization of external components

- Less than 10uW of power consumption at no load

**Figure 1-1 Application Block Diagram**

The objectives of this research project were the following:

- 1. Design a Power Management Integrated Circuit (PMIC) that satisfies the specifications presented above using a 0.8µm BiCMOS process.

- 2. Proceed with the fabrication process of the IC.

- 3. Apply a validation procedure to the IC. The goal is to provide data about the obtained performance and compare it with the simulator results.

### 1.2 Content Organization

The research discussion is divided into five chapters. Chapter 2 discusses a literature overview in which the different topologies used for this application are explained. In addition, the system architecture is proposed after researching the literature. The system design stage is discussed in detail in Chapter 3; in which each system component's circuits are explained either from the schematic and layout perspectives. The simulation and experimental data is presented in Chapter 4 with the purpose of comparing them and generating conclusions about the system's functionality. The conclusions are presented in Chapter 5 after analyzing all the simulation and experimental collected data.

## **Chapter 2 : Previous Works & Architecture Selection**

This research's topic will be the design and optimization of voltage regulators for low power applications. With the purpose of selecting the proper circuit architecture to achieve the specifications presented in section 1.1, the literature in DC/DC converters for low power applications was reviewed. The review findings are summarized in section 2.1 along with the additional analysis done for this research's objectives. Section 2.2 offers the analysis and discussion of the selected architecture to implement the PMIC proposed in this research.

### 2.1 Literature Review & Topologies Overview

Voltage regulators can be classified in three fundamental topologies: linear regulators, switching regulators (inductive), and charge pumps (capacitive). Linear regulators are limited to step-down conversion and exhibit poor efficiencies, hence are not suitable for the target application. An analysis of inductive and capacitive converter will follow, with the objective of selecting the topology that best suits the outlined specifications.

Capacitive voltage regulators have been studied by decades, but they aren't as common as the inductive ones. This is due to the fact that the capacitive regulators are used mostly in low power applications, usually microwatts. They can be designed as step up or step down. For example, a capacitive step up regulator was designed for 697 $\mu$ A nominal load with 95% of efficiency [2]. Also other capacitive regulators where designed as step up for loads of 111 $\mu$ A [3] and 10 $\mu$ A [4] and efficiencies of 78% and 97% respectively. Step down capacitive regulators has been also designed, like the ones designed for nominal loads of 11 $\mu$ A [4] and 18mA [5].

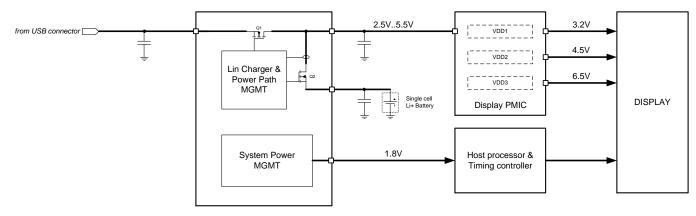

The fundamental topology of the capacitive regulator is the "Dickson Charge Pump", shown in Figure 2-1. The output voltage  $V_{OUT}$  is regulated by sending charge packages between stages. The digital signals  $\Phi$ , which has a logic high greater than the threshold voltage  $V_T$  of the diodes, are alternated each stage to provided current path between capacitors. The output voltage is controlled by the frequency at which this charge transitions between capacitors occurs. Equation (1) describes the efficiency n of this topology, where N is the quantity of stages,  $V_T$  is the forward voltage of the diodes, f is the frequency of operation, C is the stage capacitance,  $\alpha$  is the rate of the parasitic capacitances with respect to C,  $V_{IN}$  is the input voltage and  $I_{OUT}$  is the load current [6].

#### **Figure 2-1 Dickson Charge Pump**

$$n = \frac{(N+1) - \frac{(N+1)V_T}{V_{IN}} - \frac{NI_{OUT}}{fCV_{IN}}}{(N+1) + \frac{f\alpha CV_{IN}}{I_{OUT}}N}$$

(1)

The efficiency is influenced by many parameters, some of them physical like  $V_T$  and  $\alpha$ ; and others by design like  $V_{IN}$ , C, N, and f. One of the disadvantages of this topology is that the efficiency depends on the load and the input voltage; which are two variable parameters in the specifications. Also, to minimize the effect of  $V_{IN}$  and load in the efficiency very large stage capacitances are needed, therefore increasing the area of the device.

#### **Inductive Converters**

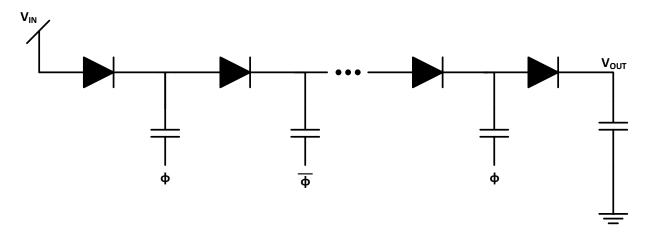

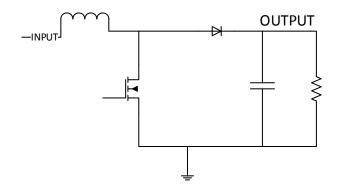

There are different topologies of inductive converters. Like the capacitive converters, they can be used as step up or step down. The fundamental topologies of this type of converter are the "Buck Converter" and the "Boost Converter". There are other topologies, but usually they are based on these two fundamental topologies. The diagrams of these two fundamental topologies are shown in Figure 2-2 and Figure 2-3. Their operation consists on managing the stored energy in the inductor magnetic field allowing a fix output voltage independently of the output load.

Figure 2-2 Buck Converter

**Figure 2-3 Boost Converter**

The inductive converter's operation modes could be classified in two when considering the behavior of the inductor current. These two modes are: continuous and discontinuous conduction modes (CCM and DCM respectively). In CCM the inductor current is always positive and greater than zero; while in DCM the inductor current reaches zero. This system will be forced to operate in DCM due to the very low load currents in the specifications. This could be proven with Equation (2) [7], because the K value of this converter will be so small that there won't be any possible value of D to satisfy the CCM criterion. This is important to be known when designing the system controller. Working in DCM has the advantage of simplifying the implementation of a digital control; therefore avoiding the use of oscillators and decreasing the quiescent losses.

$$K > K_{crit} \quad for \ CCM \tag{2}$$

$$K = \frac{2Lf_{s}I_{L}}{V_{out}} \quad \& \quad K_{crit} = 1 - D$$

In Equation (2), D is the "duty cycle" or the fraction of time that the inductor is being charged assuming CCM, L is the inductance,  $I_L$  is the load current, V is the output voltage, and  $f_s$  is the frequency of operation. If the value of K is less than the value of K<sub>crit</sub> the converter will be forced to operate in DCM; otherwise it will be operating in CCM. It can be noticed that when the output current increases, the converter is nearer to CCM operation. Although this K<sub>crit</sub> changes for some topologies, the criterion for DCM is always the same. The only difference between topologies will be the definition of K<sub>crit</sub>. Table 1 shows the CCM-Gain, DCM-Gain, and K<sub>crit</sub> expressions for each basic topology.

| Converter  | Kcrit                  | CCM-Gain         | DCM-Gain                              |

|------------|------------------------|------------------|---------------------------------------|

| Buck       | 1 - D                  | D                | $\frac{2}{1+\sqrt{1+4\frac{K}{D^2}}}$ |

| Boost      | D (1 - D) <sup>2</sup> | $\frac{1}{1-D}$  | $\frac{1+\sqrt{1+4\frac{D^2}{K}}}{2}$ |

| Buck-Boost | $(1 - D)^2$            | $-\frac{D}{1-D}$ | $-\frac{D}{\sqrt{K}}$                 |

**Table 1 Switching Converters Gain Equations**

#### Single-Inductor-Multiple-Output (SIMO) Converters

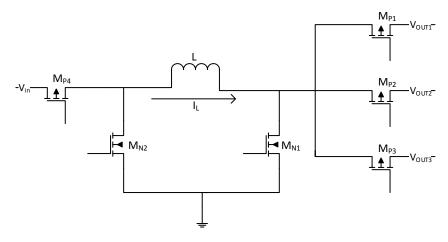

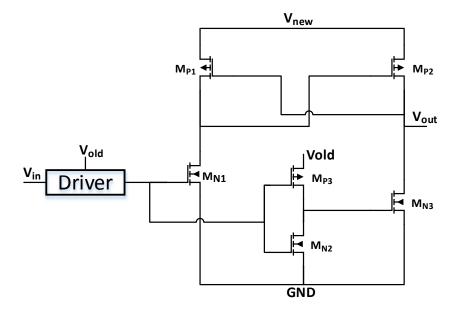

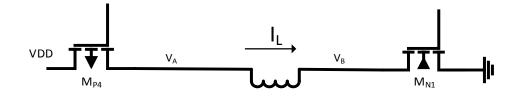

The main objective of this research is to develop a solution that minimizes the quantity of external components. This makes the "Single-Inductor-Multiple-Output" (SIMO) topology the best option. A SIMO Buck-Boost serves as both, step-up and step-down converters, [8] therefore being the viable alternative. A circuit schematic of the SIMO Buck-Boost is shown in Figure 2-4. Its operation is the same of a single buck-boost converter, which consist on managing the stored energy in the inductor magnetic field. Its three outputs switches M<sub>P1</sub>, M<sub>P2</sub>, and M<sub>P3</sub> provides current path to all the outputs; therefore enabling it to manage all of them.

Figure 2-4 SIMO Buck-Boost Converter

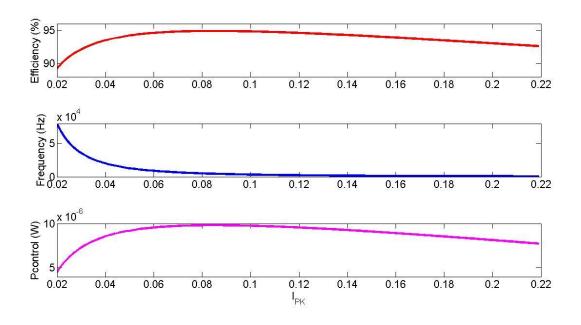

Although SIMO converters have been studied extensively, most of them focus on designs targeting loads in the milliamps or higher. SIMO converters with efficiencies of 80% [9] and 93% [10] were designed, although in the milliamps range. By using the equations presented in [10] and [11] (shown in Table 2), and transforming them assuming a one output SIMO, it is possible to derive an expression for the efficiency assuming typical values of parasitic resistances and capacitances. In Table 2  $I_{PK}$  is the inductor peak current,  $D_1$  and  $D_2$  are the energization and denergization fraction of time, respectively, with respect to the frequency of operation f, ttrans is the switching time, VIN is the input voltage of the converter, Iload is the load current of the stage; and R<sub>L</sub>, R<sub>C</sub>, R<sub>se</sub>, R<sub>sde</sub> are the internal resistances of inductor, output capacitor, energization switches, and denergization switches respectively. The resulting equations showed that it is possible to design a SIMO converter with efficiency between 85% and 95% (Figure 2-5), being the 95% the maximum efficiency point (MEP) in the frequency domain. The optimal point is the inflection point in which the switching and conduction losses are equalized due to the operation frequency. The P<sub>control</sub> plot is shown also in Figure 2-5 having 10µW, its maximum, at the MEP. This P<sub>control</sub> plot was calculated assuming target efficiency  $(\eta_{\text{target}})$  of 85%.

|                      | Name                               | Expression                                                                          |

|----------------------|------------------------------------|-------------------------------------------------------------------------------------|

| η                    | Maximum Efficiency                 | $\frac{P_{OUT}}{P_{OUT} + P_{COND} + P_{SWITCH} + P_{Control}}$                     |

| P <sub>control</sub> | Controller Power Available         | $P_{OUT}\left(\frac{1-\eta_{target}}{\eta_{target}}\right) - P_{COND} - P_{SWITCH}$ |

| PCOND                | Conduction Losses                  | $P_L + P_C + P_{SW,COND}$                                                           |

| PSWITCH              | Switching Losses                   | $I_{PK}t_{trans}f(V_{IN}+V_{OUT})$                                                  |

| PL                   | Inductor Losses                    | $R_L I_{L,RMS}^2$                                                                   |

| Pc                   | Output Capacitor Losses            | $R_C I_{C,RMS}^2$                                                                   |

| P <sub>SW,COND</sub> | Switches Conduction Loss           | $2R_{se}I_{se,RMS}^2 + 2R_{sde}I_{sde,RMS}^2$                                       |

| I <sub>L,RMS</sub>   | Inductor RMS Current               | $\frac{I_{PK}\sqrt{D_1 + D_2}}{\sqrt{3}}$                                           |

| I <sub>se,RMS</sub>  | Energization Switches RMS Current  | $\frac{I_{PK}\sqrt{D_1}}{\sqrt{3}}$                                                 |

| I <sub>sde,RMS</sub> | Denergization Switches RMS Current | $\frac{I_{PK}\sqrt{D_2}}{\sqrt{3}}$                                                 |

| I <sub>C,RMS</sub>   | Output Capacitor RMS Current       | $\frac{I_{PK}\sqrt{D_2}}{\sqrt{3}} + I_{LOAD}\sqrt{1 - D_2}$                        |

| f                    | Frequency of operation             | $\frac{V_{IN}D_1}{LI_{PK}}$                                                         |

## Table 2 SIMO Converter Efficiency Equations

Figure 2-5 SIMO Converter Efficiency Equations Plot

From the literature and theoretical review, the SIMO Buck-Boost converter predominated due to the good output regulation and external components minimization. But such DC-DC converter needs a controller to keep its functionality as discussed previously. A controller architecture is proposed in section 2.2 for the SIMO Buck-Boost converter operating in DCM.

### 2.2 Proposed Architecture

As discussed in the previous section, SIMO converters offer high efficiency while minimizing the external components, hence are best suited for the target application. Voltage regulation of the SIMO converter for the intended loads ( $\sim 25\mu A$ ) will inevitably be in discontinuous mode, as explained in section 2.1.

When operating the SIMO converter in DCM, the stored energy can be delivered to the load in two modes: sequential and distributive. In the Sequential Mode all the energy stored in the inductor during a switching cycle is sent to a single output. Opposed to this, in the Distributive Mode the energy stored in the inductor is sent to every output whenever a switching cycle occurs. It has been shown that Sequential mode has less cross-regulation problems than the Distributive Mode due to its good isolation between the outputs. The advantage of the Distributive Mode is that it has less switching losses than the Sequential mode, because its frequency of operation is usually slower than in the other mode; hence increasing the efficiency [8][12].

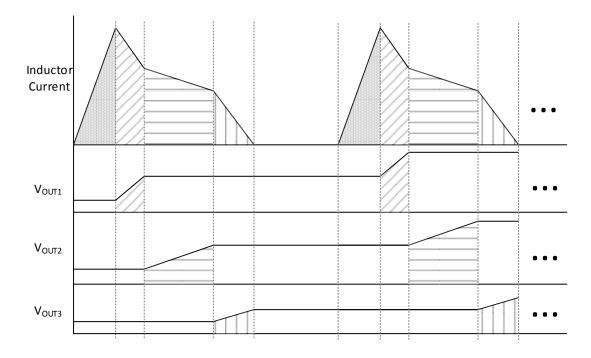

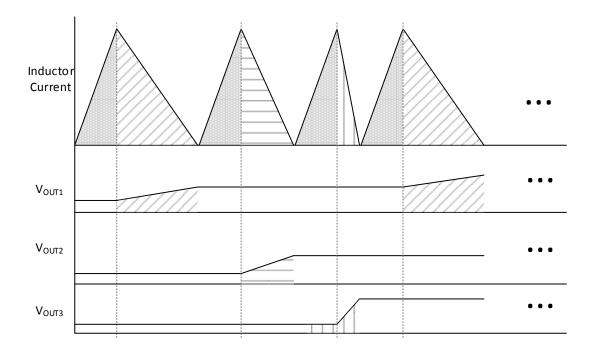

Figure 2-6 shows a time diagram of the Distributive mode of operation, assuming the SIMO Buck-Boost of Figure 2-4 is been used. Every time that the inductor reaches a peak value, energy is sent to all the outputs, in this case  $V_{OUT1}$  to  $V_{OUT3}$ . The inductor current increases when the transistors  $M_{P4}$  and  $M_{N1}$  are turned on while all the other transistors remain off, this being the energization stage. Right after the inductor reaches its peak current, energy is sent to the outputs by turning off  $M_{P4}$  and  $M_{N1}$ , and turning on  $M_{N2}$  and the transistors  $M_{P1}$  to  $M_{P3}$ , depending on which output is receiving the inductor energy. As mentioned before, this operation modes results in less switching cycles, therefore reducing the conduction losses; this with the price of having less isolation between outputs.

Figure 2-6 SIMO Distributive Mode Time Diagram

In the sequential mode the inductor is charged until its current reaches a peak current value, like in the distributive mode, but in this mode all the energy is sent only to one output. This is shown in Figure 2-7, which is a time diagram of this operation mode. It could be noticed that three switching cycles are needed to send energy to every output. This increases the switching losses with respect to the distributive mode previously discussed, but more output isolation is achieved; which is an important design specification of this device. The output isolation is achieved due to the fact that whenever an output is disabled, the system just ignores it and focus in the other two outputs; while in the distributive mode every output needs to receive energy every switching cycle.

Due to the specifications of high efficiency, it's convenient to use the Distributive Mode to reduce the switching losses. But the Distributive Mode requires every output to receive a portion of charge each switching cycle, and the system could have some of the outputs disabled. This fact makes impossible the use of a pure Distributive operation. For this reason it was decided to use a hybrid between Distributive and Sequential modes; therefore having the benefits of both of them, good outputs isolation and less switching losses.

Figure 2-7 SIMO Sequential Mode Time Diagram

The hybrid operating mode will take from the sequential mode the characteristic of ignoring an output whenever it is disabled, or energy isn't needed there. This will give the device the output isolation that is required by the specifications. From the distributive mode, the ability of sending energy to more than one output during the same switching cycle is adopted; but being optional. This means that the converter don't have to send charge to all the outputs every switching cycle, the converter just has to do it when it's required. As shown in Figure 2-8, which is the time diagram for the hybrid mode, there is a priority order for the outputs. The highest priority output is V<sub>OUT3</sub>, followed by V<sub>OUT1</sub>, and being the last one V<sub>OUT2</sub>. In the time diagram, the first three switching cycles are dedicated to V<sub>OUT3</sub>, until it crosses with its reference voltage, which is the value to which V<sub>OUT3</sub> have to be regulated. After this crossing occurs, the second priority output V<sub>OUT1</sub> receives energy. Before the switching cycle is finished V<sub>OUT1</sub> crosses its reference voltage, therefore immediately passing the priority to  $V_{OUT2}$ ; which receives energy during the same switching cycle. This is the characteristic adopted from the distributive mode. When no energy is needed in any output the system passes to the freewheeling stage, hence forcing the inductor current to zero. This stage will be active until energy is needed again in an output.

#### Figure 2-8 Hybrid Mode Time Diagram

As shown in Figure 2-8, the operation of the hybrid mode consists on charging and discharging an inductor. The inductor current is increased to a value called Inductor Peak Current (IPK) and decreased to ideally zero. For this reason an inductor current sensing circuit is needed to detect such current values, and therefore be able to implement a controller. The inductor current could be measure by invasive and non-invasive ways. The invasive current sensing circuit requires being in series along the current path, in this case the inductor. The disadvantage of this approach is that there are conduction losses due to the internal resistance of the sensor. On the other side, the non-invasive current sensing circuits can measure a current without interfering with the current path. This method is a research topic since it is the most efficient manner to sense a current and there are many ways to implement it. In this design the inductor current needs to be measured to detect two instants, the instant when the inductor current reaches IPK and the instant when the inductor current reaches zero (ZCD).

A non-invasive topology is proposed for detecting the IPK and ZCD instants based on [12] and [13]. Current-voltage converters, dynamic voltage reference generators, and hysteretic comparators are used for the implementation of such current sensors; and they are discussed in detail in Chapter 3.

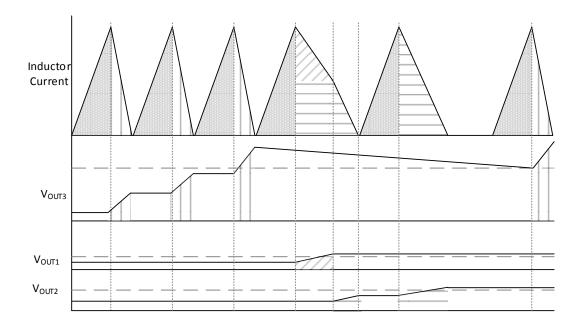

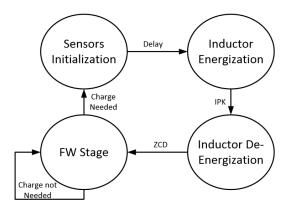

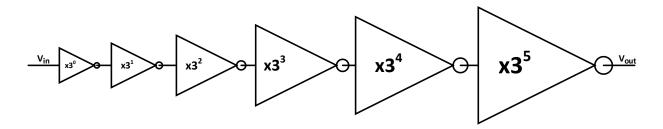

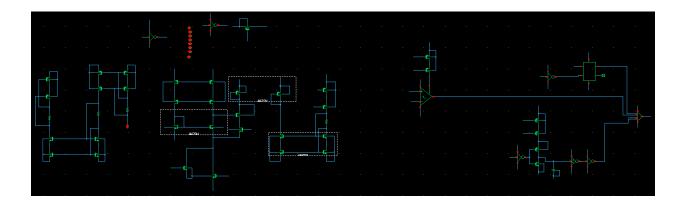

A digital controller was implemented to control the system due to its very DCM operation. If the system is operated with conventional PWM (Pulse Width Modulation) the resulting ton (energizing time) would be very small and very difficult to be implemented. For this reason a fixed peak inductor current controller was selected. Although this type of controller can be implemented using an oscillator, the use of an Asynchronous State Machine was selected to avoid the use of a high frequency oscillator, and the DC losses generated by using it. A similar controller was implemented in [14], but for milliamps loads. The state machine uses the IPK and ZCD current sensing modules to control the energizing and de-energizing times of the inductor; and distributes the energy stored in the inductor to the system's outputs. Figure 2-9 shows the state diagram of the proposed state machine controlling the inductor switching cycles. When the system is turned on, it immediately goes to the "Inductor Energization" stage, in which only switches  $M_{P4}$  and  $M_{N1}$  are turned on. This stage will remain active until IPK signal is activated meaning that the inductor peak current was reached. After this occurs, the "Inductor Deenergization" stage is started by turning on only the M<sub>P1</sub>, or M<sub>P2</sub>, or M<sub>P3</sub> and M<sub>N2</sub> switches. This stage is when the energy stored in the inductor is delivered to the output terminals. When the ZCD signal is activated, meaning that zero inductor current was reached, this phase is terminated and the "FW stage" is started. In this stage the M<sub>P5</sub> transistor, or freewheeling (FW) switch, is turned on to short the inductor terminals and avoid oscillations after ZCD is reached. This stage will remain active until any of the output comparators signals is activated; meaning inductor energy is needed in an output. During this stage all the components of the controller are put in standby mode to reduce DC losses.

Figure 2-9 State Machine's State Diagram

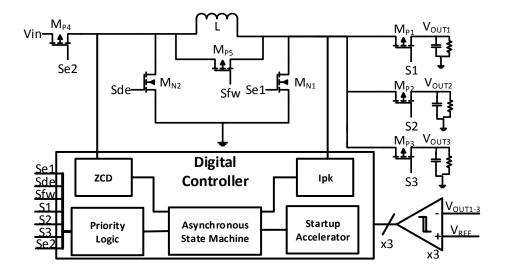

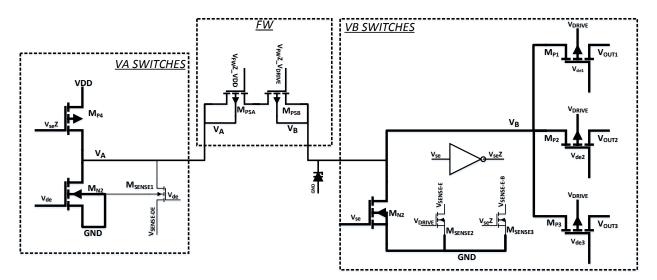

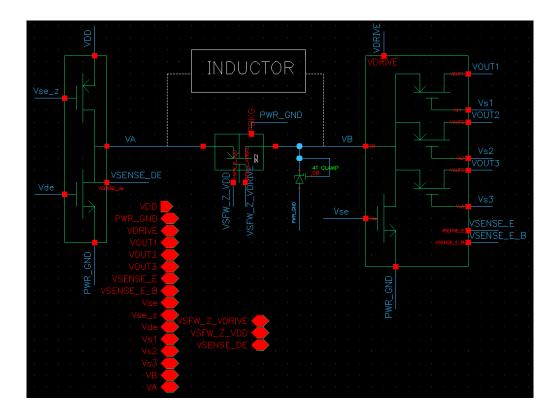

Figure 2-10 shows the SIMO converter presented in Figure 2-4 but including the proposed controller block diagram with its components. Further information of device design process is discussed in Chapter 3.

Figure 2-10 SIMO Converter Topology and Controller

#### **Design Challenges**

Some of the challenges of this design involve the implementation of very low power consumption components. Current Sensing, Comparators, and Reference System components need to be designed for a global power consumption of less than  $10\mu$ W to keep the target efficiency of 85%. To implement these very low power consumption components techniques like very high resistances and dynamic powering should be used. Very high resistances are used in the Reference System; and all the current sensing and comparators components are implemented using the dynamic powering technique.

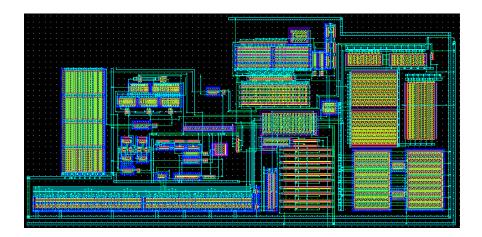

## Chapter 3 : System's Design & Components Overview

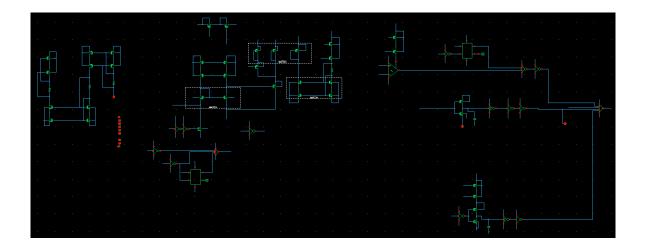

A PMIC was designed to supply three totally individual outputs. To do this the architecture presented in Figure 2-10 was used. As discussed previously, it is a complex architecture due to its novel components. This chapter discusses in detail the circuit schematics, design process, and circuit layouts of the different sub-circuits inside the proposed PMIC. The system's design was done using Computer Aided Design (CAD) and a 0.8µm BiCMOS process. Since the device is very complex, its design was divided in modules. This chapter shows all the modules and components designed along with their layout design.

### 3.1 System's Components Overview

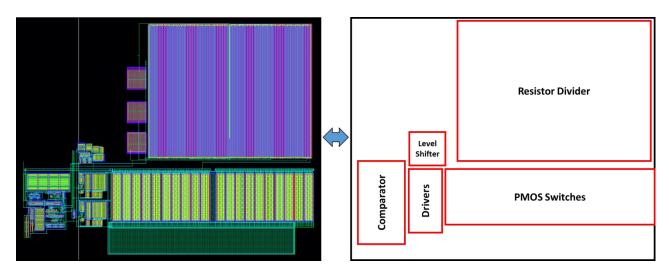

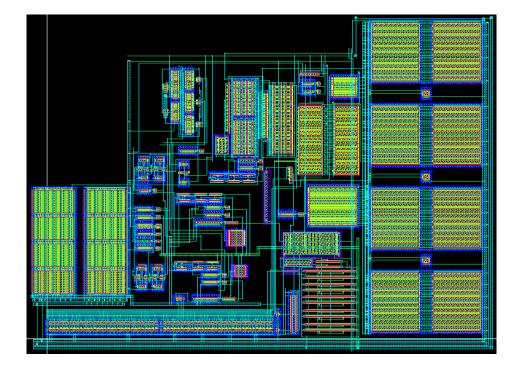

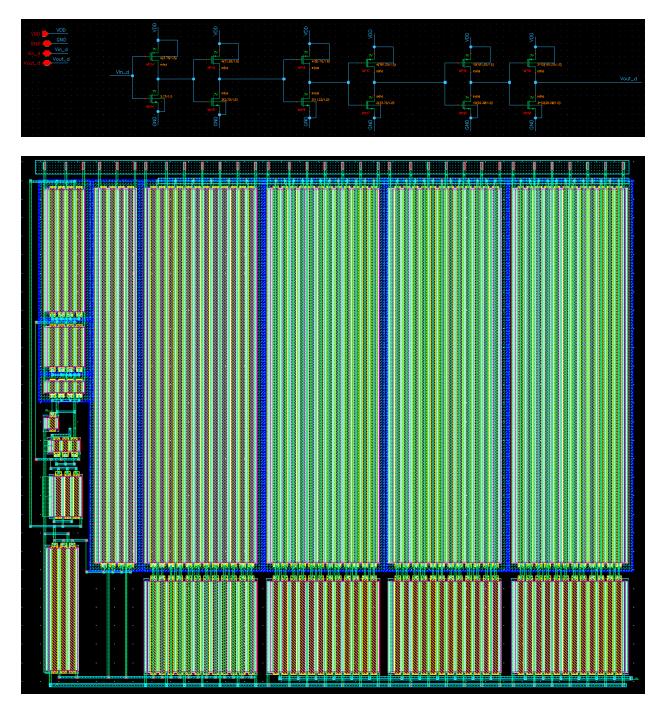

Due to the system complexity, the design stage was implemented modularly. There are two main modules, which are the Power Module and the Controller Module. The Power Module includes the power transistors and their gate drivers. From Figure 2-10, those power transistors are M<sub>N1</sub>, M<sub>N2</sub>, M<sub>P1</sub>, M<sub>P2</sub>, M<sub>P3</sub>, M<sub>P4</sub>, and M<sub>P5</sub>. All the other components of the system are included inside the Controller Module. Figure 3-1 shows the module map of the device.

Figure 3-1 Device's Map of Modules

Each component of the device is discussed in detail on this chapter. The list of modules and sub-modules is shown in Table 3, along with their accomplished specifications. If the power consumption of each controller module is added, a total of  $10.28\mu$ W is obtained; which is exactly the power budget for the controller calculated in Figure 2-5. The design procedure done to get those accomplished specifications is discussed in detail in the next sections, which discusses it one module per section. Although schematics are shown in this chapter, they are to illustrate the design. Therefore simplified schematics are shown in this section; and the real CAD schematics are shown along with their respective layouts in Appendix A – Cellviews and Layouts.

| Module         | Accomplished<br>Specs | Value                            | Module's Purpose                             |

|----------------|-----------------------|----------------------------------|----------------------------------------------|

| Reference      | VREF                  | 1.22V +/- 7%                     | Generates the voltage and current            |

| System         | Iref                  | 70nA                             | references needed by the system              |

| Bystem         | PC*                   | 0.840µW                          | Tereferees needed by the system              |

|                | IPK                   | FAST Mode $\rightarrow$ 800mA    | Provides the system with an inductor         |

| Inductor Peak  |                       | Steady State $\rightarrow$ 400mA | current value detector that sends a signal   |

| Current Sensor | PC*                   | 2.95µW                           | when the IPK value is reached during the     |

|                | i c                   | 2.55μ ₩                          | energization stage                           |

| Zero Current   | ZCD                   | 0A +/- 100mA                     | Detects the point when the current           |

| Detector       | PC*                   | 2.80µW                           | decreases near to zero during the de-        |

| Detector       | I C                   | 2.00µ W                          | energization stage                           |

| Logic          | PC*                   | 0.23µW                           | Contains the Asynchronous state machine      |

| Logic          |                       |                                  | and the priority logic                       |

| Charge         | PC*                   | 2.76µW                           | Monitors the 3 outputs to determine if they  |

| Monitor        | 10                    |                                  | need more energy to raise its voltage        |

| VDRIVE         | PC*                   | 0.70µW                           | Provides the highest voltage of the system   |

| Selector       |                       |                                  | from the supply or either from the 6.5V      |

| Beleetor       |                       |                                  | output                                       |

|                |                       |                                  | Transform a digital signal with a logic      |

| Level Shifters | nifters PC*           | 0.18µW                           | level "A" into a signal with a logic level   |

|                |                       |                                  | "B"                                          |

|                | Rise-Fall             | 2 ns                             | Provide isolation between controller and     |

| Drivers        | Times                 |                                  | power stage, and the enough current to       |

| Dirvers        | PC*                   | 0.55µW                           | change the voltage in the power transistors' |

|                |                       |                                  | gates                                        |

| Switches       | Rinternal             | [200 - 550] mΩ                   | Contains all the power transistors along     |

| Switches       | Ninternal             |                                  | with the protective diodes                   |

## Table 3 Module Design Specifications

\* PC: Power Consumption at nominal corner

### 3.2 Reference System (Refsys)

The purpose of this component is to generate the voltage and current references needed by the system. It generates a 1.22V band-gap voltage reference and a 70nA constant-to-temperature current that is mirrored to serve as 12 current sinks for the system's components. A totally independent amplifier is used as buffering for the reference voltage to an external pin. This module has the ability to change the system's reference from the internal band-gap voltage reference or either an external reference; and it's selected through a digital enable pin.

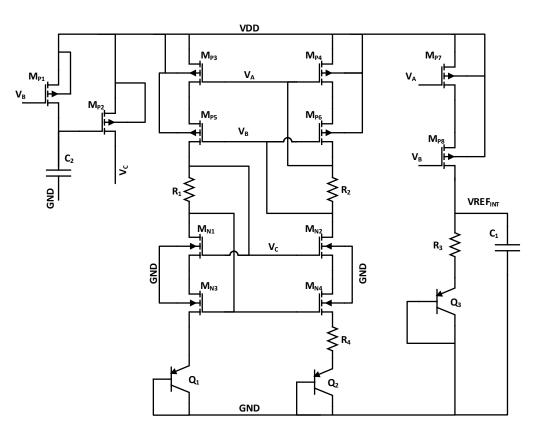

The 1.22V reference voltage directly influences the output regulation of the system because it is used as reference by the output comparators. Due to this fact, it should have a very low error percentage at every corner to accomplish with the output regulation specifications. To implement this voltage reference a double-cascode PTAT current generator was used along with BJT transistors. Figure 3-2 shows the simplified schematic of the band-gap voltage reference generator.

Figure 3-2 Internal Reference Voltage Schematic

VREF<sub>INT</sub> is the band-gap reference voltage; and it is generated by adding negative and positive Temperature Coefficients (TC). The positive TC is provided by the thermal voltage (V<sub>T</sub>) and the negative TC is generated by the base-emitter voltage V<sub>be</sub> of transistor Q<sub>3</sub>. The equation of the current flowing through transistor M<sub>P7</sub> is shown in Equation (3). It can be shown that the same current passes through resistor R<sub>3</sub> [15], assuming that transistors M<sub>P3</sub> = M<sub>P4</sub>, M<sub>P5</sub> = M<sub>P6</sub>, M<sub>N1</sub> = M<sub>N2</sub>, and M<sub>N3</sub> = M<sub>N4</sub>; and all of them are operating in saturation region. In Equation (3), A<sub>Q1</sub> and A<sub>Q2</sub> are the respective transistors Q<sub>1</sub> and Q<sub>2</sub> areas; and V<sub>T</sub> is the thermal voltage. The voltage VREF<sub>INT</sub> is equal to the addition of the voltage drops V<sub>beQ3</sub> in transistor Q<sub>3</sub> and in R<sub>3</sub>, which is equal to I<sub>MP7</sub> multiplied by the value of resistor R<sub>3</sub>; as shown in Equation (4).

$$I_{MP7} = V_T \frac{1}{R4} \ln\left(\frac{A_{Q2}}{A_{Q1}}\right)$$

$$VREF_{INT} = V_T \frac{R_3}{R_4} \ln\left(\frac{A_{Q2}}{A_{Q1}}\right) + V_{beQ3}$$

(4)

If the partial derivative over temperature is taken to Equation (4), the relation shown in Equation (5) is obtained. To achieve TC cancellation the rate between resistors  $R_3$  and  $R_4$  should be set, along with the natural logarithm of  $N = A_{Q2}/A_{Q1}$ , equal to the value shown in Equation (6).

$$\frac{\partial VREF_{int}}{\partial T} = \frac{\partial V_{be}}{\partial T} + \frac{R_3}{R_4} ln(N) \frac{\partial V_T}{\partial T}$$

(5)

$$\frac{R_3}{R_4} ln(N) = \frac{-\frac{\partial V_{be}}{\partial T}}{\frac{\partial V_T}{\partial T}}$$

(6)

$M_{P1}$ ,  $M_{P2}$ , and  $C_2$  form the startup circuit of the PTAT current generator. When the circuit is turned on, meaning VDD goes from zero to the supply voltage,  $V_C$  node will be charged through  $M_{P2}$ . This will force the NMOS transistors  $M_{N1}$ ,  $M_{N2}$ ,  $M_{N3}$ , and  $M_{N4}$  to conduct current and find and stable operation point. When capacitor  $C_2$  is completely charged to VDD through transistor  $M_{P1}$ ,  $M_{P2}$  will remain off while VDD remains high. The capacitor  $C_2$  is designed to allow enough time to  $M_{P2}$  to start the circuit. The resistors  $R_1$  and  $R_2$  are designed to set the appropriate bias voltages for the PTAT current generator cascode-stages.

This reference system has the feature of switching between two different references, the internal one discussed above and an external one. The reference to be used is controlled by an

external pin called VREF\_EXT\_EN. When this pin is high, connected to VDD, the external reference is used by the system. If the external reference enable pin is connected to GND then the internal reference will be used by the system. This was implemented by using CMOS transmission gates.

With the objective of monitoring the internal reference voltage externally, a buffer was used to replicate it to the output pin VREF\_OUT. This was done because the rail current flowing through  $M_{P7}$  is in the nano-amperes range being this not enough to charge the enormous pin capacitance. A simple two stage amplifier was designed to be connected as buffer. The bias current for the amplifier is provided by a second PTAT current generator dedicated only to this purpose. It has very low rail currents and it's almost the same first PTAT circuit of Figure 3-2.

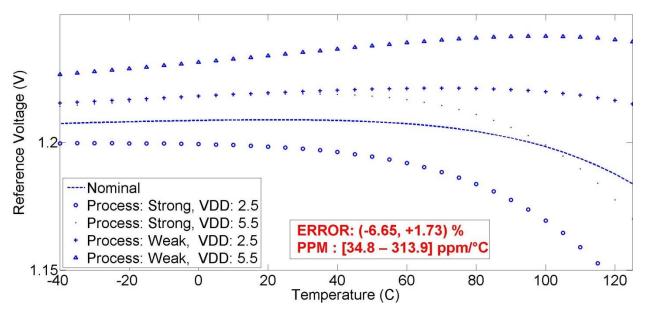

Simulations were done to the reference system to check its performance in quiescent current and error percentage. DC sweeps were done to verify the error percentage of the internal reference voltage varying the supply voltage (VDD), the temperature, and the process. The supply voltage was varied in 3 discrete steps, which are 2.5V, 3.6V, and 5.5V. The two opposite corners of process, which are weak and strong inversions, were used with each VDD corner. A Temperature-DC sweep was simulated to verify the reference voltage error percentage at every corner. Figure 3-3 shows the temperature sweep of the reference voltage. The error percentage value of VREF is (-6.65, +1.73) %. The weak process is the principal responsible of the negative error percentage.

Figure 3-3 Reference Voltage Temperature-DC Sweep

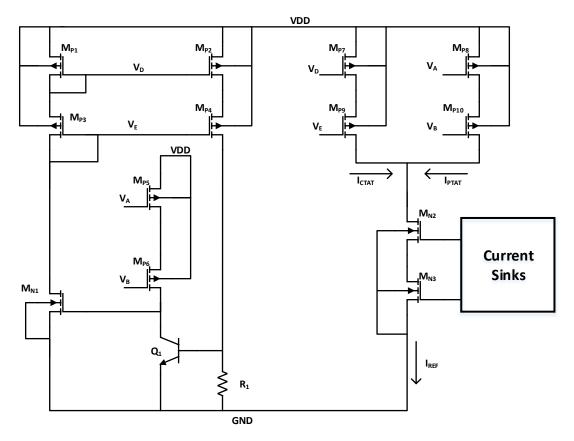

Reference currents are provided by this module to different components. Some of them as the Charge Monitor module don't need a very precise reference; but others like the current sensing modules need a very precise current reference to be accurate. If the current reference varies with temperature, a proportional variation will be seen in the inductor peak current and zero current values; therefore degrading the optimal inductor current control and the systems efficiency. To avoid that variation, a constant-to-temperature current reference needed to be designed. This was implemented by adding a Complementary-to-Temperature (CTAT) current reference to the PTAT current reference generated in the internal reference circuit of Figure 3-2. The CTAT generator used in this design is shown in Figure 3-4 along with the CTAT and PTAT current adder and the current sinks.

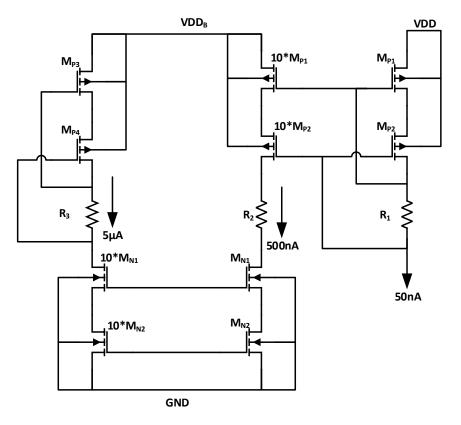

**Figure 3-4 Current Reference Generator Schematic**

This schematic assumes that  $M_{P1}=M_{P2}=M_{P7}/1.5$ ,  $M_{P3}=M_{P4}=M_{P9}/1.5$ ,  $M_{P8}=M_{P5}$  and  $M_{P10}=M_{P6}$ ; from which  $M_{P8}$  and  $M_{P10}$  also are equal to  $M_{P4}$  and  $M_{P6}$  of Figure 3-2 respectively. Transistor  $M_{P5}$  is a mirror of the PTAT current that forces a multiplier of the PTAT current to flow through transistor  $Q_1$ . The  $V_{ce}$  voltage of  $Q_1$  turns on the transistor  $M_{N1}$ ; and with it the cascaded-mirror formed by  $M_{P1}$ ,  $M_{P2}$ ,  $M_{P3}$ , and  $M_{P4}$  starts flowing current. That current flowing through transistors  $M_{P2}$  and  $M_{P4}$  is described by Equation (7), where  $V_{be,Q1}$  is the base-emitter voltage of transistor  $Q_1$ . Due to this direct proportionality of  $I_{MP4}$  to a base-emitter voltage, which has a negative TC, it's called a Complementary-to-Temperature (CTAT) current.

$$I_{MP4} = \frac{V_{be,Q1}}{R_1}$$

(7)

The value of this current is settled by R<sub>1</sub> to achieve I<sub>REF</sub> TC cancellation, described by Equation (8), which is the addition of I<sub>PTAT</sub> and I<sub>CTAT</sub> currents. This differential equation is valid only assuming that  $\frac{\partial R_1}{\partial T} = 0$ , which could be very small depending the process. R<sub>1</sub> value is

calculated by Equation (9), where  $TC_{PTAT}$  is the chosen value when VREF<sub>INT</sub> was designed in Equation (5); which is obtained by setting the I<sub>REF</sub> TC to zero and solving Equation (8) for R<sub>1</sub>.

$$\frac{\partial I_{REF}}{\partial T} = \frac{\partial I_{PTAT}}{\partial T} + \frac{\partial I_{CTAT}}{\partial T} = \frac{\partial I_{PTAT}}{\partial T} + \frac{1}{R_1} \frac{\partial V_{be,Q1}}{\partial T}$$

$$R_1 = \frac{1}{-\frac{\partial I_{PTAT}}{\partial T}} \frac{\partial V_{be,Q1}}{\partial T}$$

(9)

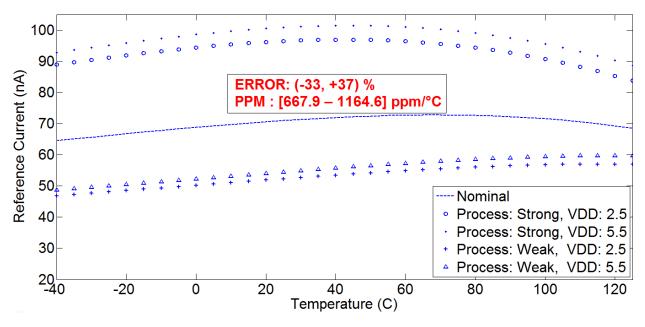

Temperature sweeps were done to verify reference and supply currents performance. Figure 3-5 shows the temperature sweep for the reference current  $I_{REF}$ . At the nominal corner the  $I_{REF}$  is hold near 70nA over the entire temperature window. But two groups of current data are with positive and negative offset over the nominal corner; and these variations are due to process variations.  $I_{REF}$  variation would have been much larger if the TC cancellation hasn't been implemented. That could be noticed in the parabolic shapes of the plot, which shows that the changes in current aren't proportional to temperature changes.

Figure 3-5 Reference Current Temperature-DC Sweep

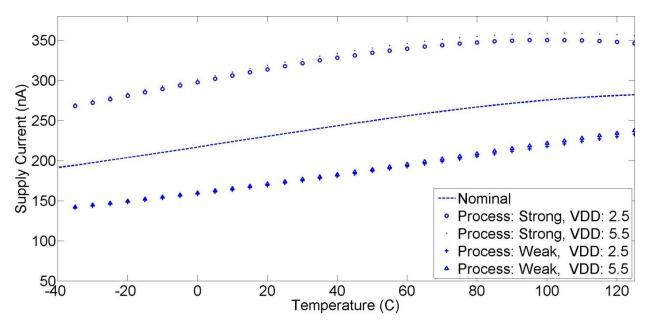

In order to implement an efficient reference system, its current consumption should be the minimum. To corroborate this fact, temperature sweeps were done in different supply voltages and processes corners; and the results are shown in Figure 3-6. Assuming from the plot 300nA maximum current at nominal temperature, the maximum power loss due to the reference system operation could be calculated. If the maximum supply voltage (5.5V) is multiplied by 300nA, a maximum power of  $2\mu W$  is needed to operate the reference system at nominal temperature. Since the power budget for the controller of  $10\mu W$  hasn't been overpassed even at the worst case scenario of VDD, it could be concluded that power consumption accomplishes the specifications. In addition, the average reference system power consumption at nominal corner was verified using transient simulations, an as shown in Table 3, the result was 840nW; which leaves enough power budget for the rest of the modules.

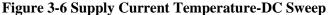

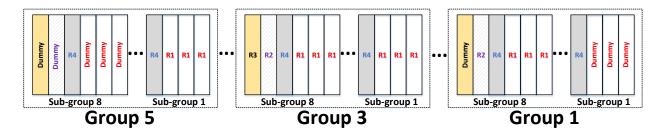

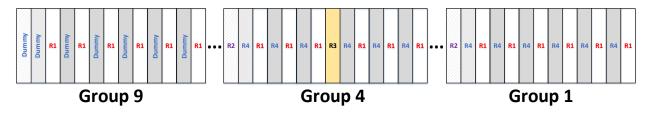

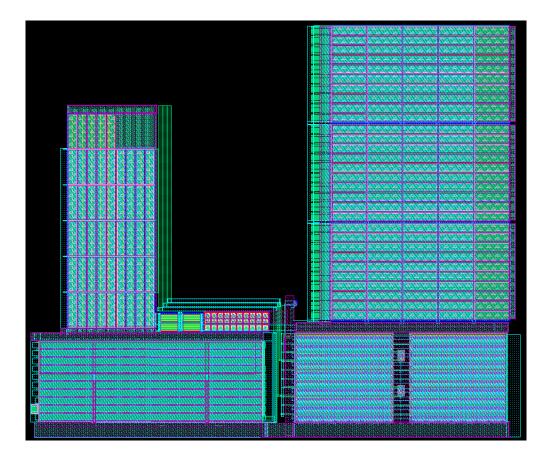

This module's layout is located almost in the center of the device. This was done to avoid product fabrication damage to it. Its layout is shown in Figure 3-7 along with its three main components identified. As explained above, those main components are the internal reference voltage generator, the CTAT current generator, and the reference voltage buffer. The layout design was emphasized in symmetry between components with rates; like the transistors Q<sub>1</sub> and Q<sub>2</sub>, and resistors R<sub>3</sub> and R<sub>4</sub> of Figure 3-2. These components has directly influence on the bandgap-voltage, or reference voltage, as shown previously in Equation (4). To achieve perfect symmetry, dummy transistor, resistors, and capacitors were used. Figure 3-8 shows the distribution used for resistors R<sub>3</sub> and R<sub>4</sub>. The values of R<sub>4</sub> and R<sub>3</sub> are 3.2M $\Omega$  and 17.5M $\Omega$ respectively. They were distributed as serpentine by dividing R<sub>4</sub> in 15 fingers of 213.333k $\Omega$ ; and R<sub>3</sub> in 80 fingers of 218.750k $\Omega$ . To achieve a 1 to 4 correspondence between the resistors, 5 dummy fingers of R<sub>4</sub> were added.

Figure 3-7 Reference System's Layout

| R4        | R4        | R4        | R4        |

|-----------|-----------|-----------|-----------|

| R3        | R3        | R3        | R3        |

| R3        | R3        | R3        | R3        |

| R3        | R3        | R3        | R3        |

| <b>R3</b> | <b>R3</b> | R3        | <b>R3</b> |

| R4        | R4        | R4        | R4        |

| <b>R3</b> | <b>R3</b> | R3        | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | R3        | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | R3        | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | R3        | <b>R3</b> |

| R4        | R4        | R4        | R4        |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | R3        | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | R3        | R3        |

| R4        | R4        | R4        | Dummy     |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | R3        |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| Dummy     | Dummy     | Dummy     | Dummy     |

| R3        | <b>R3</b> | R3        | R3        |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

| <b>R3</b> | <b>R3</b> | <b>R3</b> | <b>R3</b> |

Figure 3-8 R3 and R4 Resistors Matching Distribution for Internal Reference Voltage

In Figure 3-2, transistor  $Q_2$  has 10 times the emitter area of  $Q_1$ . For every BJT transistor in the reference system the unit area is 7.03  $\mu$ m<sup>2</sup>. The area of  $Q_1$  and  $Q_2$  is 7.03 and 10\*7.03 um<sup>2</sup> respectively. To have a completely symmetric distribution 14 unit area BJT transistors were added to the layout as dummies. Figure 3-9 shows the  $Q_1$  &  $Q_2$  distribution for the internal reference voltage.

| Dummy | Dummy | Dummy | Dummy | Dummy |  |

|-------|-------|-------|-------|-------|--|

| Dummy | Q2    | Q2    | Q2    | Dummy |  |

| Q2    | Q2    | Q1    | Q2    | Q2    |  |

| Dummy | Q2    | Q2    | Q2    | Dummy |  |

| Dummy | Dummy | Dummy | Dummy | Dummy |  |

Figure 3-9 BJT Transistors Q1 & Q2 Distribution for Internal Reference Voltage

For the  $Q_1$  BJT transistor in the CTAT current generator no distribution is needed because there is no rate with another transistor in the CTAT current equation (Equation (7)). The same BJT transistor distribution used for the internal reference generator's PTAT was used for the reference buffer's PTAT. All the PMOS and NMOS current mirrors were distributed using interdigitation [16]. More detailed layout vs schematic components identification is shown in Appendix A – Cellviews and Layouts

### 3.3 Inductor Peak Current Sensor (IPK)

Since the operating mode of the SIMO converter, in DCM, consist on charging and discharging an inductor, meaning increasing the inductor current to an IPK value and decreasing it to ideally zero, an inductor current sensing circuit is needed to be able to implement a controller. This module provides the system with an inductor current value detector that sends a signal when the IPK value is reached during the energization stage of Figure 2-8. It consists of a non-invasive current sensor, therefore doesn't affecting the efficiency of the system's power stage. In addition, less than 50nA of quiescent current is achieved during standby mode, therefore decreasing the expected controller DC losses.

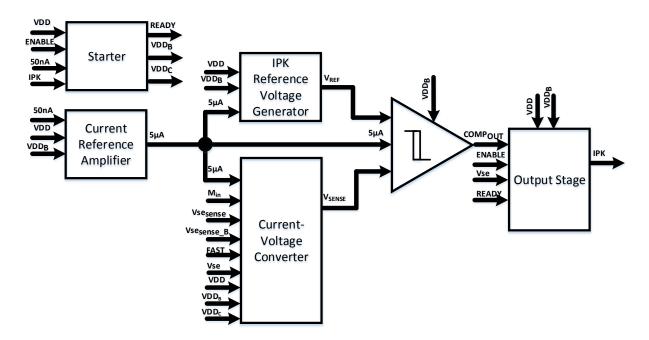

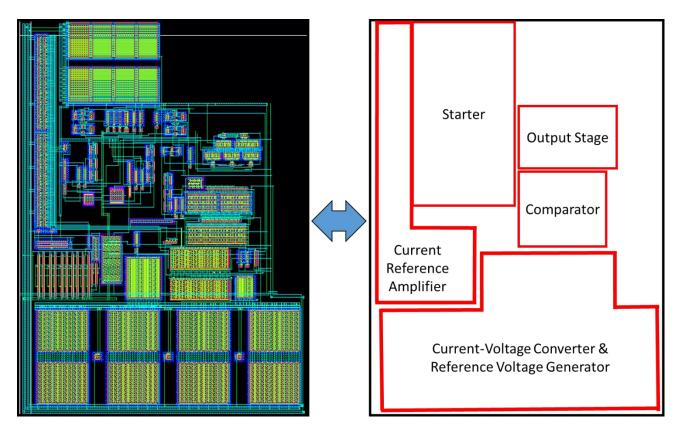

The Inductor Peak Current Sensor's block diagram is shown in Figure 3-10. It consists of six main components which are: Starter, Current Reference Amplifier, IPK Reference Voltage Generator, Current-Voltage Converter, Hysteretic Comparator, and Output Stage. Each component is discussed in detail below.

The Starter is the responsible of initializing every component when the ENABLE signal is received. This signal is turned on/off by the Logic Module in Figure 3-1, discussed in section 3.5; and it will be turned on every time a switching cycle is started. This component provides the IPK sensors with the VDD<sub>B</sub> and VDD<sub>C</sub> supply nodes; and raises the signal READY when the initialization stage is done. The Current Reference Amplifier converts a reference current of 50nA, provided by the Reference System module shown in Figure 3-1, and generates a new reference of  $5\mu A$ . The  $5\mu A$  are created only when the system isn't idle. This allows the system to have a low quiescent current. These 5µA serves as reference to the Current-Voltage Converter, IPK Reference Voltage generator, and Hysteretic Comparator components. Inductor current sensing is implemented by the Current-Voltage Converter. This component generates a voltage, the sensing voltage V<sub>SENSE</sub>, which changes linearly with respect to the inductor current. The  $V_{\text{SENSE}}$  voltage is compared with the  $V_{\text{REF}}$  voltage generated by IPK Reference Voltage Generator. The reason of using a reference voltage different from the one generated by the Reference System module of section 3.2 will be discussed below when the components' schematics are shown. A hysteretic comparator was implemented using active latches to achieve fast response when V<sub>SENSE</sub> approaches to V<sub>REF</sub>. The comparator's output COMP<sub>OUT</sub> passes

through an output stage before moving the output pin voltage IPK. The Output Stage is responsible of filtering possible spikes at IPK during the initialization stage.

Figure 3-10 Inductor Peak Current Sensor Block Diagram

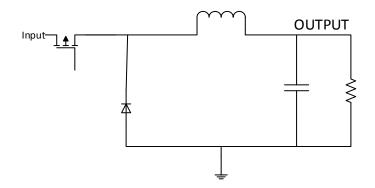

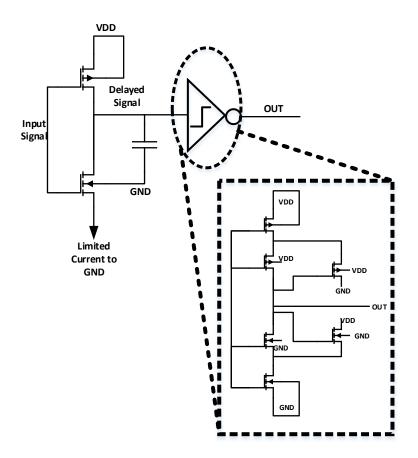

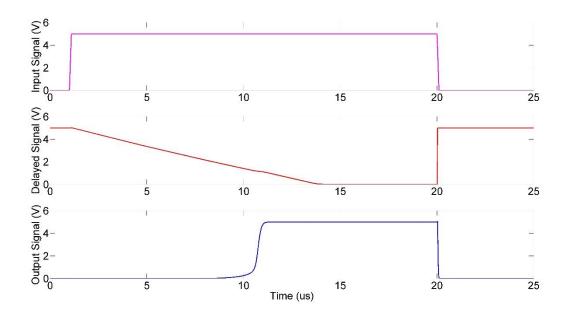

When the ENABLE signal is turned on by the Logic module, the first IPK component to work is the Starter. The Starter gives some delay time between the IPK sensor initialization and energization stage's start time. The energization stage will begin when the IPK sensor's output READY is turned on. In all the modules of this design, every delay is generated using current-limited CMOS inverters and Hysteretic CMOS inverters. A schematic of the delay circuit is shown in Figure 3-11. When a rising edge occurs at the input signal the Delayed signal node changes slowly, therefore holding the output node to GND until the delay time occurs. Figure 3-12 illustrates this scenario, in which the input, delayed, and output signals are the magenta, red, and blue plots respectively. In this case the delay time is almost 10µs, but it can be controlled with the capacitor value in the delayed signal node and with the limited current value.

Figure 3-11 Delay Circuit Low-to-High Edge

Figure 3-12 Delay Circuit Example Plot

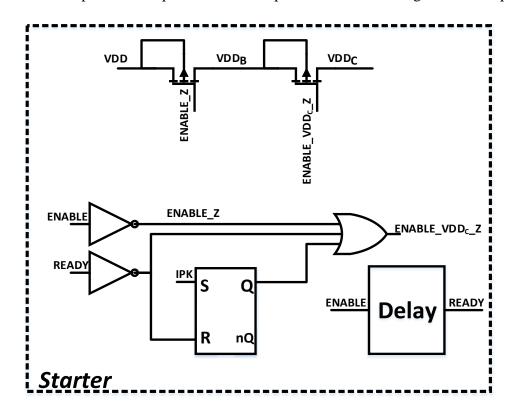

In addition to adding a delay between the ENABLE and READY signals, the Starter manages the supply nodes  $VDD_B$  and  $VDD_C$ . Figure 3-13 shows the schematic of this component. The  $VDD_B$  power comes from VDD through a PMOS switch; and  $VDD_C$  power comes from  $VDD_B$  also through a PMOS switch. Immediately after ENABLE changes to high, the signal ENABLE\_Z goes to low and  $VDD_B$  rises to the VDD voltage. This will initialize all the parts supplied by this node. Due to the fact that READY is low at the beginning, ENABLE\_VDD\_C\_Z will remain high, therefore keeping  $VDD_C$  disconnected from  $VDD_B$ . Immediately after READY goes to high, ENABLE\_VDD\_C\_Z will be low and  $VDD_C$  will be connected to  $VDD_B$ , therefore supplying the components connected to this supply node. During this time the energization starts and current sensing is running. When IPK is reached, the IPK signal will raise forcing the Q output of the Starter's latch to high, therefore blocking the supply on  $VDD_C$ . This is done to avoid current spikes during high current paths inside the Current-Voltage Converter Component. The process will be repeated each time energization is required.

Figure 3-13 IPK Starter Component Schematic

The IPK sensor module needs to have a very fast response due to the very high inductor current slope. For this reason currents in the micro-amperes range are needed to increase the slew rate of the Comparator and the Current-Voltage Converter. But using for example  $5\mu$ A of DC reference current will make the system exceed the controller's power budget of 10  $\mu$ W (Figure 2-5). This current converter (Figure 3-14), or current mirror, converts the 50nA of reference current to  $5\mu$ A when the supply VDD<sub>B</sub> is available. This supply voltage is provided by the Starter and it is available immediately after the ENABLE signal is turned on by the Logic module. The current is increased by a factor of hundred using two stages of cascoded-current mirrors with gain of 10. This occurs if the transistors sizes relations shown in the schematics are implemented. The  $5\mu$ A current is copied to other modules by mirroring the PMOS transistors MP<sub>3</sub> and MP<sub>4</sub>.

Figure 3-14 IPK Current Reference Amplifier

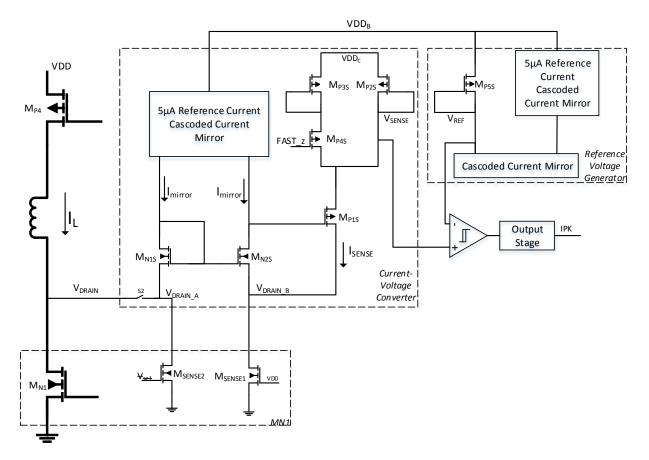

A more detailed diagram, than the one shown in Figure 3-10, of how the components of the IPK sensor interact is shown in Figure 3-15. There the supply nodes  $VDD_B$  and  $VDD_C$ , which are provided by the Starter, can be identified. When active time begins, S2 switch is turned on and the current amplifier starts to force the drain voltages of  $M_{SENSE1}$  and  $M_{N1}$  to the

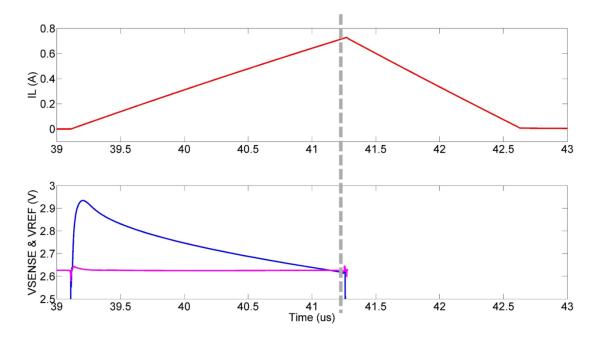

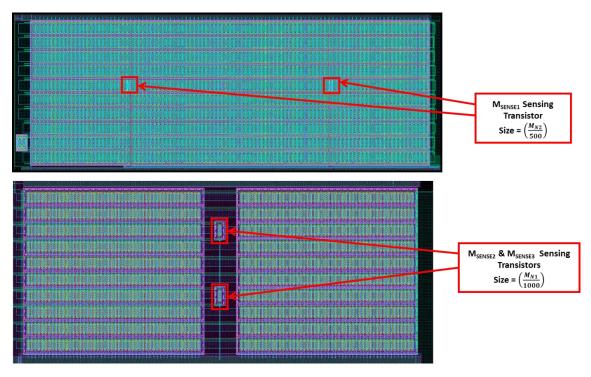

same potential. This occurs because both NMOS transistors,  $M_{N1S}$  and  $M_{N2S}$ , are operating in the saturation region while having the same drain current I<sub>mirror</sub>. Since M<sub>SENSE1</sub> is K times smaller than M<sub>N1</sub>, and both have the same potentials, its current will be smaller than I<sub>L</sub> by the same amount, as shown in Equation (10). This equation is derived from the MOSFET drain-current equation for the triode region; resulting that the ratio between I<sub>MN1</sub> and I<sub>MSENSE1</sub> is only influenced by their transistors' size. The I<sub>MSENSE1</sub> current is the addition of I<sub>SENSE</sub> and the I<sub>mirror</sub> current flowing through M<sub>N2S</sub>; and I<sub>SENSE</sub> is provided by the negative feedback loop formed by  $M_{P1S}$  and  $M_{N2S}$ . The sensing current is converted to the voltage  $V_{SENSE}$  by passing it through the diode-connected PMOS M<sub>P2S</sub>; and also M<sub>P3S</sub> when the FAST signal is on. This sensing voltage is compared with a reference voltage ( $V_{REF}$ ) generated by  $M_{P5S}$  and the 5µA current reference generated by the IPK Current Reference Amplifier. This novel V<sub>SENSE</sub> and V<sub>REF</sub> generation allows a constant peak inductor current at every supply voltage.  $V_{\text{SENSE}}$  and  $V_{\text{REF}}$  are compared with an active-latch comparator to allow high speed comparison. The inductor current at which  $V_{\text{SENSE}}$  and  $V_{\text{REF}}$  crosses will be the inductor peak current detected by the sensor; as shown in Figure 3-16 where the red, blue, and magenta graphs are the IPK current, the  $V_{\text{SENSE}}$ , and the V<sub>REF</sub> voltages respectively. This peak current can be settled by K and the ratio between M<sub>P2S</sub> and M<sub>P5S</sub>, as indicated in Equation (11); where I<sub>mirror</sub> is the current flowing through M<sub>N1S</sub> and M<sub>N2S</sub>, and  $I_{REF}$  is the 5µA current reference flowing through  $M_{P5S}$  in Figure 3-15.

$$\frac{I_{MN1}}{I_{MSENSE1}} = \frac{\left(\frac{W}{L}\right)_{MN1}}{\left(\frac{W}{L}\right)_{MSENSE1}} = K$$

$$I_{peak} = \left(\left(\frac{M_{P2S}}{M_{P5S}}I_{REF}\right) + I_{mirror}\right)K$$

(10)

(11)

Figure 3-15 IPK Current Sensor Topology Diagram

The FAST mode is activated when the system is during the startup stage. This occurs whenever any of the output voltages is below the reference voltage by more than 0.5V. During this stage the PMOS transistor  $M_{P4S}$  is active and part of the current  $I_{SENSE}$  will flow through  $M_{P3S}$ , therefore increasing the rate between  $M_{P2S}$  and  $M_{P5S}$  in Equation (11). A higher peak inductor current will be settled in this mode, therefore increasing the regulation speed of the output nodes.

Figure 3-16 Inductor Peak Current Control, VSENSE & VREF

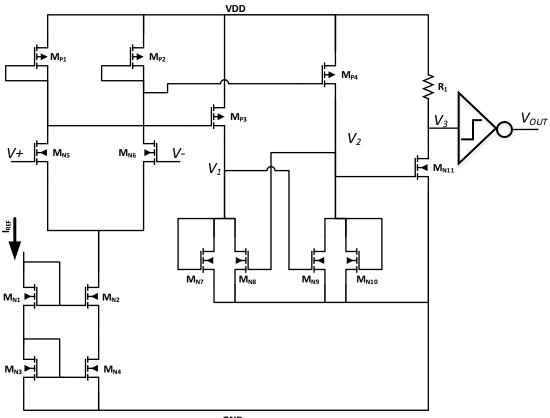

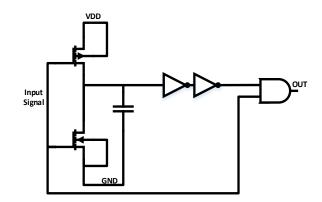

A latched hysteretic comparator, like the preamplifier presented in[17], was used to compare the  $V_{SENSE}$  and  $V_{REF}$  voltages inside the IPK current sensor. It consists of a NMOS input differential pair with active load, an active latch stage, and the Hysteretic CMOS Inverter used in the delay circuit shown in Figure 3-11. The schematic of the Hysteretic comparator is shown in Figure 3-17 along with a plot describing its operation in Figure 3-18. As shown in the plot, the comparator's response is very fast, under the 200 nano-seconds range. A minimum difference between V+ and V- signals is amplified in signals V<sub>1</sub> and V<sub>2</sub>. As the two input signals are near crossing, V<sub>1</sub> and V<sub>2</sub> nodes approaches the DC equilibrium point in which both of them have the same voltage; which is almost one volt over GND. When this point is reached, the NMOS transistor M<sub>N11</sub> will be turned on and it will pull down the V<sub>3</sub> voltage; therefore pulling up the output node V<sub>OUT</sub>.

The output stage consist of an AND gate with the objective of masking any noise during the initialization stage. It will keep the IPK output low until a  $Min_{ton}$  time, for minimum turn on time, has passed. This time is settled by a delay circuit like the one shown in Figure 3-11 but with a current source instead of a current sink.

GND

Figure 3-17 Inductor Peak Current Sensor's Hysteretic Comparator

Figure 3-18 Hysteretic Comparator Operation Plot

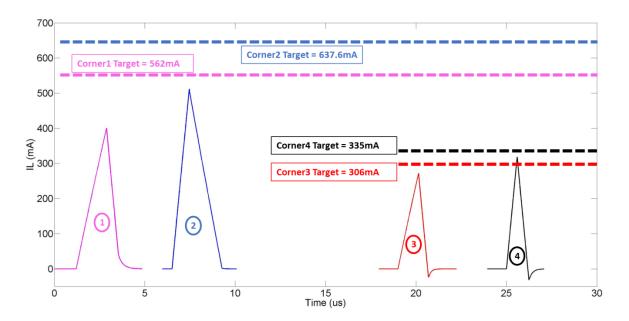

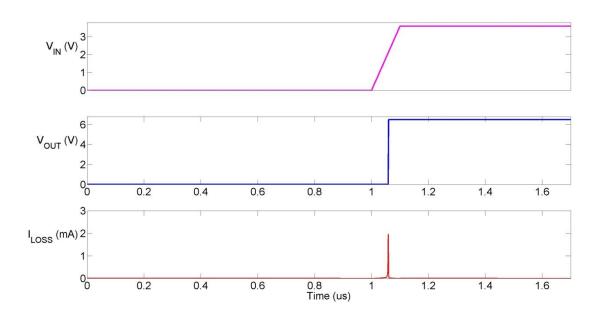

To prove the functionality and performance of the IPK current sensor, transient simulations were done at supply voltage and process corners. The supply voltage was settled to discrete steps of 2.5V and 5.5V. The two opposite corners of processes, which are weak and strong, were combined with each VDD corner. Figure 3-19 shows the performance for the 4 different corners obtained when combining the process and supply voltage variations mentioned. The plot shows the inductor current behavior during a switching cycle (solid lines), along with the expected IPK value at each corner (dashed lines), which is calculated using Equation (11) and the simulation data presented in Table 4.

As shown in this equation, the IPK value is proportional to  $I_{REF}$  and  $I_{mirror}$  therefore inducing dependence from the reference current of section 3.2; which have variation due to process as shown in Figure 3-5. This is the reason why different expected IPK values are defined for each corner. Due to this reference current variation, different IPK values results from Equation (11). The  $I_{mirror}$  and  $I_{REF}$  values for each corner are summarized in Table 4 along with the corners specifications.

But in addition to the expected IPK value variation, a negative offset from that value could be noticed in Figure 3-19, meaning that the actual IPK value is less than the expected value. From the IPK Current Sensor Topology Diagram shown in Figure 3-15, the switch S2 isn't an ideal switch; and a parasitic resistance  $R_{PAR,S2}$  exists on it. This  $R_{PAR,S2}$  creates and offset in  $V_{DRAIN_A} = V_{DRAIN_B}$  over  $V_{DRAIN}$  as described in Equation (12).

$$V_{DRAIN\_A} = V_{DRAIN} + R_{PAR,S2} I_{mirror}$$

(12)

This offset is applied to the sense transistor  $M_{SENSE1}$  drain, and the assumption of exactly same terminal voltages between  $M_{SENSE1}$  and  $M_{N1}$  isn't entirely true. Of course, the error doesn't affect the functionality for generating the sense current  $I_{SENSE}$ , but a different value of K in Equation (11) will be obtained. This K value is the ratio between  $M_{N1}$  and  $M_{SENSE1}$  transistors, as shown in Equation (10), and its value will be less than the 1000 times ratio designed. The value of K's reduction is dynamic, and it is inversely proportional to the inductor current, or  $V_{DRAIN}$ voltage; meaning that the larger the  $V_{DRAIN}$  voltage is, the smaller the error's effect would be.

The inductor peak current IPK value, including the effect of S2 switch parasitic resistance, could be calculated by Equation (13); in which  $K_{ERROR}$  is the error percentage of the K value.

$$I_{peak} = \left( \left( \frac{M_{P2S}}{M_{P5S}} I_{REF} \right) + I_{mirror} \right) K * (1 - K_{ERROR})$$

(13)

Table 4 contains the simulation data for the inductor current when the  $V_{SENSE}$  and  $V_{REF}$  voltages of Figure 3-15 are equal, "I<sub>L</sub>-Sim" column, and the results of Equation (13) for each corner. As could be noticed, these two values are very near for each corner, therefore proving the  $I_{peak}$  value equation accuracy. The  $K_{ERROR}$  is calculated using Equation (14), which depends on the ratio between the actual values of  $I_L$  and the addition of  $I_{SENSE}$  and  $I_{mirror}$ .

$$\frac{\left(1000 - \left(\frac{I_L}{I_{SENSE} + I_{mirror}}\right)\right)}{1000} = K_{ERROR}$$

(14)

| Corner | Process | VDD | I <sub>mirror</sub> | I <sub>ref</sub> | Isense | I∟-Sim  | Kerror | IL-EQ  | IPK-EQ | IPK-Sim |

|--------|---------|-----|---------------------|------------------|--------|---------|--------|--------|--------|---------|

| Ur     | nits    | VDD |                     | μΑ               |        | mA      |        | mA     |        |         |

| 1      | Strong  | 2.5 | 48.02               | 4.8              | 506.51 | 373.57  | 33%    | 378.70 | 562.15 | 400.4   |

| 2      | Strong  | 5.5 | 52.03               | 5.5              | 588.61 | 467.64  | 27%    | 465.44 | 637.63 | 510.37  |

| 3      | Weak    | 2.5 | 26.313              | 2.6              | 277.27 | 226.718 | 25%    | 228.75 | 306.31 | 273.03  |

| 4      |         | 5.5 | 27.5                | 2.9              | 312.93 | 259.856 | 24%    | 256.30 | 335.77 | 318     |

**Table 4 IPK Simulation Data**

The columns IPK-EQ and IPK-Sim in Table 4 show the data of the IPK calculation using Equation (11) and the IPK data from the simulations. The simulation data for IPK value shows that it is greater than the current when  $V_{SENSE}$  and  $V_{REF}$  are the same; being the delay of the Comparator response the responsible one.

Although the real IPK value is less than the expected one, it doesn't affect the functionality of the device. This is because the error is negative and no excessive inductor current, that could damage the device, is reached. On each corner, the error in the IPK value is less than  $100\mu$ A, which represents 0.016% of the IPK value.

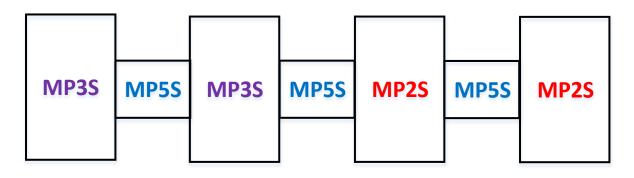

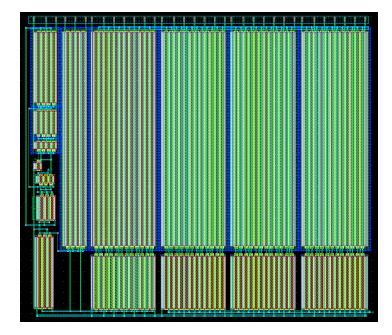

This module's layout is located right down of the Reference System's layout, as shown in Figure 3-1. It was intentionally located near the reference system, far from the power stage, to avoid noise due to power paths. Matching was considered between the Current-Voltage Converter and the Reference Voltage Generator; specifically between PMOS transistors  $M_{P2S}$ ,  $M_{P3S}$ , and  $M_{P5S}$  of Figure 3-15. These three transistors were symmetrically distributed as shown in Figure 3-21. As in all the modules, every transistor current mirror was matched using the interdigitation method[16]. The NMOS transistors  $M_{SENSE1}$  and  $M_{SENSE2}$  in Figure 3-15, which are K times smaller than power transistor  $M_{N1}$ , are located in the  $M_{N1}$  module in Figure 3-1 to achieve good matching between them. The location of the IPK sensor's components in the layout is shown in Figure 3-20. More detailed layout vs schematic components identification is shown in Appendix A – Cellviews and Layouts.

Figure 3-20 Inductor Peak Current Sensor's Layout

Figure 3-21 IPK Current-Voltage Converter & Reference Voltage Generator Matching

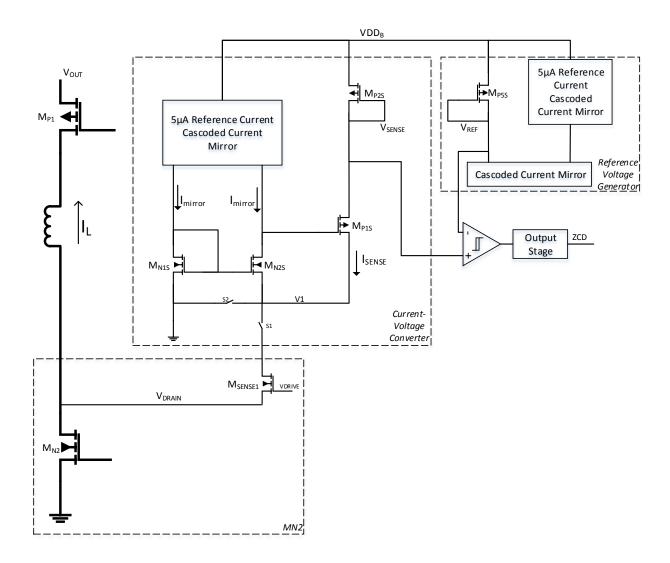

## 3.4 Zero Current Detector (ZCD)

After inductor peak current value is reached, de-energization stage will begin and inductor current will start decreasing. If it overpasses much below zero then efficiency will be degraded because the negative inductor current will be provided by the output capacitors. For this reason a very precise zero current detector (ZCD) is needed to avoid negative inductor currents. A similar IPK topology was implemented to detect the point when the current decreases near to zero; but using the approach presented in [13]. The same standby zero current loss of IPK is required for this module to maintain a very low quiescent current, and therefore not exceed the controller power budget in Figure 2-5.

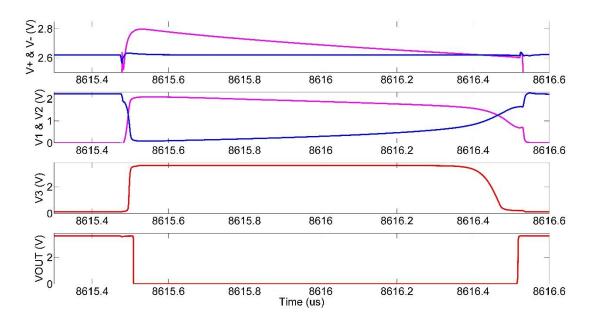

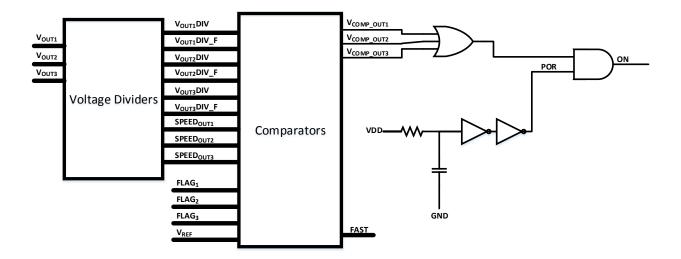

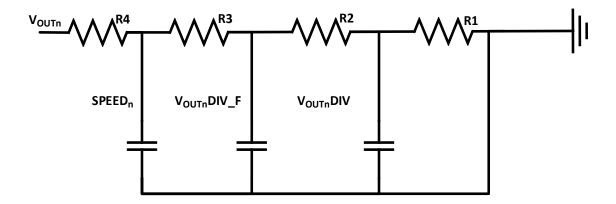

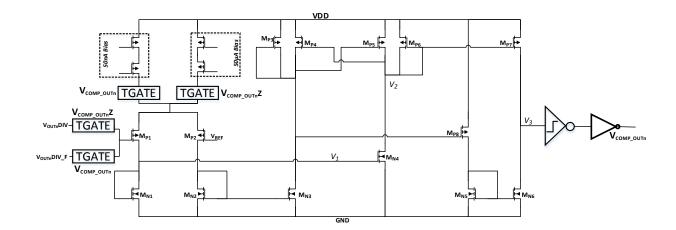

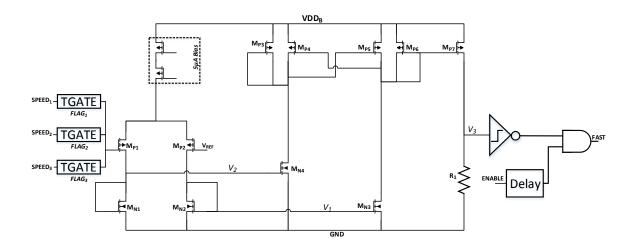

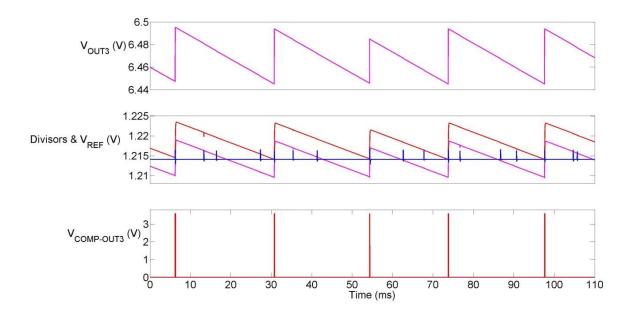

The same block diagram of Figure 3-10 could be used to describe the ZCD module, but without the Starter module. It's not needed because this module is initialized with the same ENABLE signal provided to the IPK sensor, therefore being initialized at the same instant that the IPK sensor initializes. Then when the de-energization stage is started, the ZCD module is already initialized.