## HIGH-LEVEL PARTITIONING OF DISCRETE SIGNAL TRANSFORMS FOR DISTRIBUTED HARDWARE ARCHITECTURES

By

Rafael A. Arce Nazario

A thesis submitted in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### COMPUTING AND INFORMATION SCIENCE AND ENGINEERING

## UNIVERSITY OF PUERTO RICO MAYAGÜEZ CAMPUS

June, 2007

Approved by:

Domingo Rodríguez, Ph.D Member, Graduate Committee

Dorothy Bollman, Ph.D Member, Graduate Committee

Rogelio Palomera, Ph.D Member, Graduate Committee

Isidoro Couvertier, Ph.D Member, Graduate Committee

Manuel Jiménez, Ph.D President, Graduate Committee

Nazario Ramírez, Ph.D Representative of Graduate Studies

Nestor Rodríguez, Ph.D Chairperson of the Department Date

Date

Date

Date

Date

Date

Date

Abstract of Dissertation Presented to the Graduate School of the University of Puerto Rico in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

### HIGH-LEVEL PARTITIONING OF DISCRETE SIGNAL TRANSFORMS FOR DISTRIBUTED HARDWARE ARCHITECTURES

By

Rafael A. Arce Nazario

June 2007

Chair: Manuel Jimenez, Ph.D Major Department: Computing and Information Science and Engineering

Discrete signal transforms (DSTs) have numerous applications in a wide spectrum of scientific fields. To attain superior performance, the size and composition of these algorithms frequently require implementation to architectures involving more than one dedicated hardware device. Even though hardware implementations of signal processing algorithms are known to be orders of magnitude faster than most other generic computing platforms, they are not commonplace mainly because of the increased complexity involved in partitioning and mapping such algorithms onto distributed hardware platforms. Automated methods and tools to aid in the design and exploration of distributed implementations shall encourage adoption of dedicated hardware platforms for high-performance applications.

Traditionally, partitioning to distributed hardware architectures (DHAs) has been done either manually, or at various stages of the design process, predominantly at the behavioral and structural levels. Although these schemes have produced acceptable implementations, they do not necessarily exploit the functional properties of algorithms. Structural level techniques handle the design at an abstraction level too low for the algorithm functionality to be effectively interpreted. Most proposed higher-level strategies target generic partitioning problems through local optimization techniques, which miss out on alternate formulations that become apparent only on a higher level of abstraction.

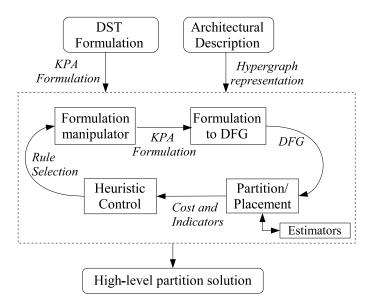

This dissertation presents an automated methodology specifically designed for partitioning DSTs onto DHAs. The methodology takes advantage of DST features at two levels of abstraction: the graph and algorithmic levels. At the algorithmic level, an exploration is conducted in search of equivalent transform formulations that are more suitable for the target topology. At the graph level, a series of DSTspecific structural considerations are made to improve the partitioning heuristic. The developed strategy integrates several algorithms which allow exploring partitioning solutions at both abstraction levels.

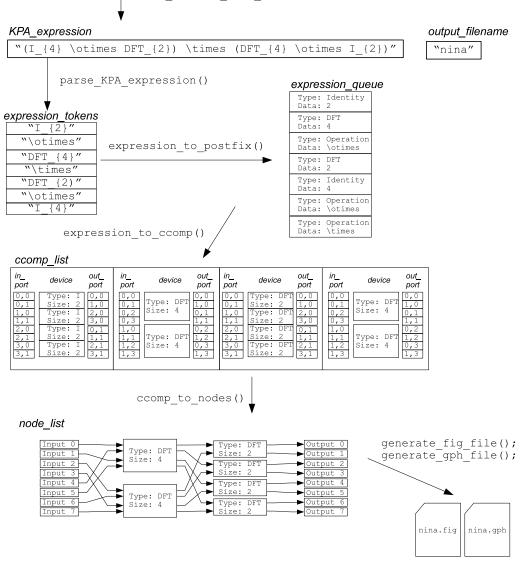

A Kronecker products algebra (KPA) to dataflow graph conversion (DFG) tool was developed to allow straightforward conversion and structural visualization of KPA expressed formulations. The DFG generated by this tool is partitioned using a k-way deterministic algorithm with structural considerations derived from common DST features. A scheduler estimates latency of the partition solution, constrained by the available computational resources, as determined by an area estimator. Solution cost at the graph level is used to transform the current DST formulation, and thus explore alternative formulations as part of the partition optimization process. Given the exponential size of the space of equivalent formulations, a greedy, polynomialtime exploration heuristic was designed.

Results from the application of this methodology to a range of sizes of Discrete Fourier Transforms and Discrete Cosine Transforms evidence the advantages of making the partition methodology DST-aware. Latency and run-time reductions of up to 34% and 99%, respectively were obtained with respect to previously proposed, stochastic high-level partitioning approaches. Resumen de Disertación Presentado a Escuela Graduada de la Universidad de Puerto Rico como requisito parcial de los Requerimientos para el grado de Doctor en Filosofía

### PARTICIONAMIENTO A ALTO NIVEL DE TRANSFORMADAS DISCRETAS DE SEÑALES A ARQUITECTURAS DE HARDWARE DISTRIBUIDO

Por

Rafael A. Arce Nazario

Junio 2007

Consejero: Manuel Jimenez, Ph.D Departamento: Ciencias e Ingeniería de la Computación y la Información

Las transformadas de señales discretas (TSDs) tienen numerosas aplicaciones en una ámplia gama de campos científicos. Para lograr obtener un mayor rendimiento, frecuentemente se requiere la implementación de dichas transformadas en arquitecturas de múltiples dispositivos. Las implementaciones de estos algoritmos en hardware suelen obtener rendimientos significativamente mejores que otras plataformas de procesamiento general. Sin embargo, dichas implementaciones no abundan, principalmente por la complejidad necesaria para particionar estos algoritmos a plataformas de hardware distribuido y determinar las estructuras correspondientes en hardware. El desarrollo de métodos y herramientas que ayuden en el diseño y exploración de estas implementaciones facilitará la adopción de estas plataformas para aplicaciones de alto rendimiento.

Tradicionalmente, el particionamiento a arquitecturas de hardware distribuido (AHD) se ha realizado de forma manual o como parte de alguna de las etapas del diseño automatizado, tanto a alto nivel como a nivel estructural. A pesar de que dichas técnicas de particionamiento han producido resultados aceptables, en la mayoría de los casos estas no aprovechan las propiedades de estas transformadas a nivel algorítmico. Las técnicas de particionamiento a nivel estructural trabajan con una representación a un nivel de abstracción demasiado bajo como para aprovechar cualquier aspecto funcional del algoritmo. Por otro lado, las técnicas de alto nivel han sido diseñadas, en su mayoría, para casos genéricos. Esto las limita a utilizar técnicas genéricas de optimización local y por lo tanto, obvian formulaciones alternas que solo se pueden visualizar a un nivel de abstracción más alto.

Esta disertación presenta una metodología automatizada específicamente diseñada para particionar TSDs a AHDs. La metodología aprovecha características de las TSDs tanto a nivel gráfico como a nivel algorítmico. En el nivel algorítmico, se explora el espacio de formulaciones equivalentes en busca formulaciones que resulten más apropiadas para la arquitectura. A nivel gráfico, se introdujeron una serie de consideraciones a los heurísticos de particiónamiento que atienden particularidades estructurales de las TSDs. La estrategia propuesta integra varios algoritmos que permiten la exploración de soluciones en ambos niveles de abstracción. Se desarrolló una herramienta para la conversión de expresiones en álgebra de productos Kronecker (APK) a grafos de flujo de data (GFD). Esta herramienta permite conversión rápida de formulaciones de TSDs, así como la visualización de sus estructuras computacionales. El GFD traducido es particionado usando un algoritmo determinístico de particionamiento en k-partes, al que se le han añadido consideraciones estructurales de las TSDs. Un planificador ("scheduler") estima la latencia de la solución de partición, restringido por los recursos computacionales disponibles, los cuales son determinados por un estimador de área. El costo de la solución a nivel gráfico se usa para transformar la formulación algorítmica actual y así explorar otras alternativas como parte del proceso de optimización. Debido al tamaño exponencial del espacio de formulaciones equivalentes, se diseñó un heurístico de exploración ambicioso ("greedy") que tiene complejidad de tiempo polinomial.

Se utilizó la estrategia propuesta para obtener resultados del particionamiento para un rango de tamaños de transformadas discretas de Fourier y transformadas discretas de coseno. Estos evidencian las ventajas que consigue nuestra estrategia gracias a ser consciente de las características de las TSDs. Se obtuvieron reducciones en latencia y tiempo de ejecución de 34% y 99%, respectivamente, en comparación con técnicas de alto nivel anteriormente propuestas, que utilizaban estrategias genéricas y estocásticas. Copyright © 2007 by

Rafael A. Arce Nazario

This work is dedicated to Maritza, my wife, for her love and understanding, for believing in me, and helping me keep my sanity. Also, to my parents Marirosa and Rafael Angel, for instilling in me the joy of learning and the drive to excel academically. To all of them for being my role models of dedication and excellence.

#### ACKNOWLEDGMENTS

I would like to thank my doctoral advisor Dr. Manuel Jiménez for his dedication, suggestions and guidance in the present investigation. On many occasions, it was his vision and enthusiasm that helped keep this endeavor alive. I also appreciate the intellectual support and savvy advise from Domingo Rodriguez, and the valuable suggestions from rest of my graduate committee members: Dorothy Bollman, Isidoro Couvertier, and Rogelio Palomera. My appreciation to the CISE administrative staff for their help.

I would also like to thank the organizations that funded my research work: UPR-Humacao, GEM consortium, Resource Center for Sciences and Engineering, WALSAIP project, and CISE program.

Many thanks to Carmen Irizarry for providing a welcoming home during my Mayagüez stays. My appreciation to Kathy and Jerry Takaks for helping me start off this Ph. D. venture on the right foot by being such wonderful hosts in Rochester, NY.

# TABLE OF CONTENTS

| na | ge. |

|----|-----|

|    |     |

| ABSTRACT ENGLISH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ABSTRACT SPANISH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                   |  |  |

| ACKNOWLEDGMENTS ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                   |  |  |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ii                                                                                                                                                                |  |  |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | v                                                                                                                                                                 |  |  |

| LIST OF ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rii                                                                                                                                                               |  |  |

| 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                 |  |  |

| 1.1Objectives and Scope of Research1.2Dissertation Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\frac{3}{4}$                                                                                                                                                     |  |  |

| 2 Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                 |  |  |

| 2.2       Distributed Hardware Architectures       1         2.3       Partitioning to DHAs       1         2.3.1       Graph partitioning algorithms       1         2.3.2       Partitioning for Distributed Hardware Architectures       1         2.3.3       Structural partitioning       1         2.3.4       Behavioral-level Partitioning       1         2.3.5       Limitations of Previous Methods       1         2.3.6       A glimpse into our approach       2         2.4       Hardware implementation of signal transforms       2         2.4.1       General DST Definition       2         2.5       Optimizing discrete signal transform implementations for specific architectures       3 | $\begin{array}{c} 7 \\ .0 \\ .4 \\ .6 \\ .8 \\ .2 \\ .5 \\ .25 \\ .25 \\ .26 \\ .7 \\ .4 \\ .5 \\ .5 \\ .6 \\ .7 \\ .4 \\ .5 \\ .5 \\ .5 \\ .5 \\ .5 \\ .5 \\ .5$ |  |  |

| 3 Problem Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87                                                                                                                                                                |  |  |

| 3.2 Methodology $\ldots \ldots 4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87<br>10                                                                                                                                                          |  |  |

| 4 | Tools |                                                                                                |

|---|-------|------------------------------------------------------------------------------------------------|

|   | 4.1   | Kronecker Product Algebra                                                                      |

|   |       | 4.1.1 Definitions and Basic Rules                                                              |

|   | 4.2   | Stride Permutations                                                                            |

|   | 4.3   | From Kronecker Products Algebra to Dataflow Graph                                              |

|   |       | 4.3.1 Problem Formulation                                                                      |

|   |       | 4.3.2 Implementation                                                                           |

|   | 4.4   | Graph Partitioning                                                                             |

|   |       | 4.4.1 Problem Formulation                                                                      |

|   |       | 4.4.2 Algorithms for Graph Partitioning                                                        |

|   |       | 4.4.3 Preliminaries                                                                            |

|   |       | 4.4.4 Kernighan-Lin Bipartitioning Heuristic                                                   |

|   |       | 4.4.5 Fiduccia-Mattheyses                                                                      |

|   |       | 4.4.6 Simulated Annealing                                                                      |

|   |       | 4.4.7 Genetic Algorithms                                                                       |

|   |       | 4.4.8 k-way Partitioning                                                                       |

|   | 4.5   | k-way Implementation                                                                           |

|   |       | $4.5.1  \text{Cost Function}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

|   |       | 4.5.2 DST Considerations in Graph Partitioning 67                                              |

|   |       | $4.5.3  \text{Complexity}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $    |

|   | 4.6   | Scheduling                                                                                     |

|   | 4.7   | Resource Estimation                                                                            |

|   |       | 4.7.1 Architectural Model                                                                      |

|   |       | 4.7.2 Target Technology                                                                        |

|   |       | 4.7.3 Resource Estimation Model                                                                |

|   |       | 4.7.4 Module Components Resource Estimation 81                                                 |

|   |       | 4.7.5 Resource estimation scheme validation                                                    |

|   | 4.8   | Summary                                                                                        |

| 5 | Formu | lation Exploration                                                                             |

|   | 5.1   | General Considerations                                                                         |

|   | 5.2   | Experiments to Assess Effect of Transformations on Partition Qual-                             |

|   |       | ity                                                                                            |

|   |       | 5.2.1 Inter-stage Permutations                                                                 |

|   |       | 5.2.2 Kernel Granularity                                                                       |

|   |       | 5.2.3 Breakdown Strategy                                                                       |

|   | 5.3   | FFT Formulation Exploration Heuristic                                                          |

|   | 5.4   | Partitioning the Discrete Cosine Transform                                                     |

|   | 5.5   | DCT Regular Algorithms                                                                         |

|   |       | 5.5.1 Püschel's Cooley-Tukey-like DCT Algorithms 109                                           |

|   |       | 5.5.2 Hsiao and Tseng's DCT Algorithm                                                          |

|   |       | 5.5.3 Morikawa's Simple Structured Fast DCT algorithm 112                                      |

|   |       | 5.5.4 Nikara's Perfect Shuffle DCT Algorithm                                                   |

|   | 5.6   | CT-like Decomposition for NPS-DCT                                                              |

|     | $5.7 \\ 5.8$      | Experiments119Summary121                                                                                       |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------|

| 6   | Result            | ts and Analysis                                                                                                |

|     | 6.1               | Graph Considerations1236.1.1 Initial Partitioning Solution1236.1.2 Stage-limited Node Swapping124              |

|     | 6.2               | Effect of Formulation Exploration                                                                              |

|     | 6.3               | Comparison Against Established Methodology1286.3.1 Srinivasan's DFGP Methodology1286.3.2 Results Comparison130 |

|     | 6.4               | Scaling the Suboptimality                                                                                      |

|     | 6.5               | Summary                                                                                                        |

| 7   | Concl             | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $138$                                    |

|     | 7.1<br>7.2<br>7.3 | Contributions                                                                                                  |

| 8   | Ethics            | 8                                                                                                              |

| APF | PENDI             | <b>CES</b>                                                                                                     |

| А   | Proto             | type Documentation                                                                                             |

|     | A.1               | Kronecker to dataflow graph tool (KTG)                                                                         |

|     | A.2               | A.1.2 KTG implementation functions and data structures 155<br>Graph partitioning heuristic                     |

|     | 11.2              | A.2.1 Usage                                                                                                    |

|     |                   | A.2.2 DGP prototype functions and data structures                                                              |

|     | A.3               | DMAGIC                                                                                                         |

|     |                   | A.3.1 Usage                                                                                                    |

| В   | CT-lil            | FFT formulation derivation                                                                                     |

|     | Refere            | ences                                                                                                          |

| סות |                   |                                                                                                                |

| ыО  | GKAP              | HICAL SKETCH                                                                                                   |

## LIST OF TABLES

| Table | page                                                                                         |

|-------|----------------------------------------------------------------------------------------------|

| 5-1   | Results for granularity experiment                                                           |

| 5-2   | Results of FFT formulation exploration for various FFT sizes targeting<br>a 4-Ring topology  |

| 5–3   | Results of FFT formulation exploration for various FFT sizes targeting<br>a 4-Array topology |

| 5–4   | Latency in c-steps for various sizes of DCT formulations                                     |

| 5–5   | Execution time in seconds for various sizes of DCT formulations 121                          |

| 6–1   | Formulation exploration heuristic performance - 4-Ring topology 127                          |

| 6–2   | Formulation exploration heuristic performance - 4-Array topology 127                         |

| 6–3   | FFT Results of SBPH vs. our methodology, assuming no concurrency. 131                        |

| 6–4   | FFT Results of SBPH vs. our methodology, assuming concurrency 132                            |

| 6–5   | DCT Results of SBPH vs. our methodology, assuming no concurrency. 132                        |

| 6–6   | DCT Results of SBPH vs. our methodology, assuming concurrency 132                            |

| 6–7   | Run times for DCT                                                                            |

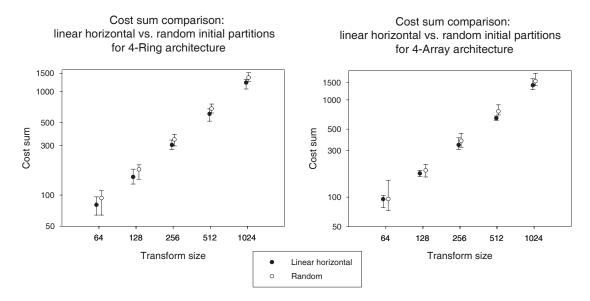

| 6–8   | Suboptimality comparison based on cost sums for 4-Ring topology 134                          |

| 6–9   | Suboptimality comparison based on cost sums for 4-Array topology 134                         |

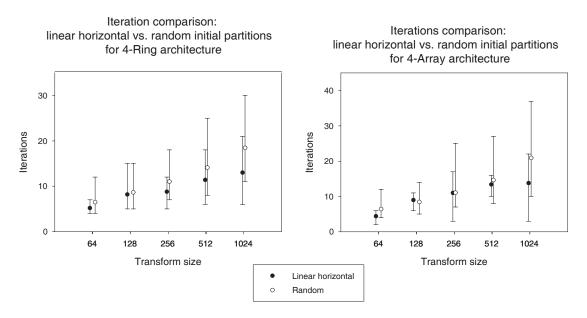

| 6-10  | Suboptimality comparison based on latency for 4-Ring topology 136                            |

| 6-11  | Suboptimality comparison based on latency for 4-Array topology 136                           |

## LIST OF FIGURES

| Figure |                                                                                                                                                       | page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

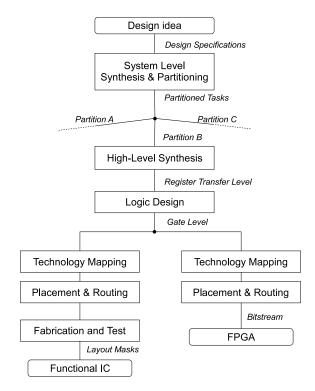

| 2-1    | Flow for Computer Aided Design for VLSI                                                                                                               | 8    |

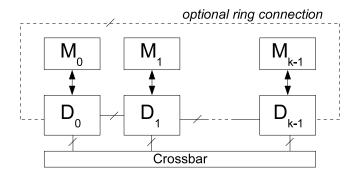

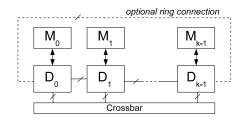

| 2-2    | General architectural model for a distributed hardware architecture                                                                                   | 13   |

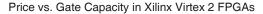

| 2–3    | Price vs. capacity for Xilinx Virtex 2 FPGAs. Source: www.digikey.com                                                                                 | 13   |

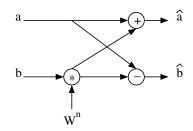

| 2-4    | Dataflow graph representation of the radix-2 butterfly                                                                                                | 28   |

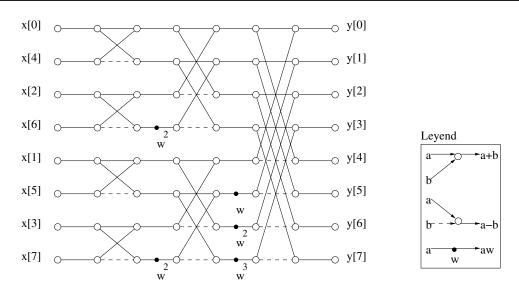

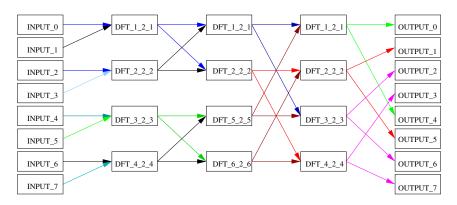

| 2–5    | Data flow for an 8-point FFT. Dashed lines represent operands that<br>will be subtracted. Filled dots represent multiplication by twiddle<br>factors. | 29   |

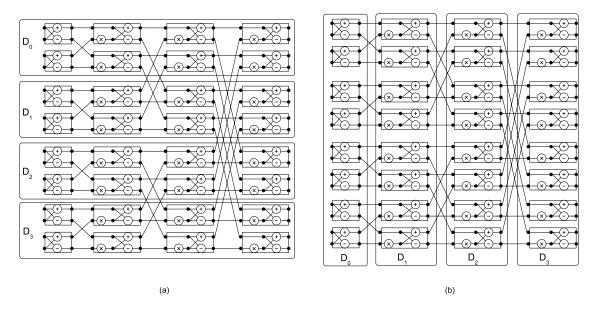

| 2-6    | A one-to-one mapping of a 16-point FFT to a 4-FPGA platform                                                                                           | 30   |

| 2-7    | Folding of an 8-point FFT: (a) fully expanded DFG, (b) strict hori-<br>zontal folding and (b) strict vertical folding.                                | 31   |

| 2-8    | Single kernel implementation of FFT                                                                                                                   | 32   |

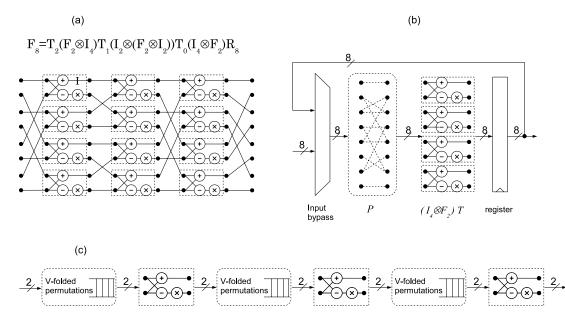

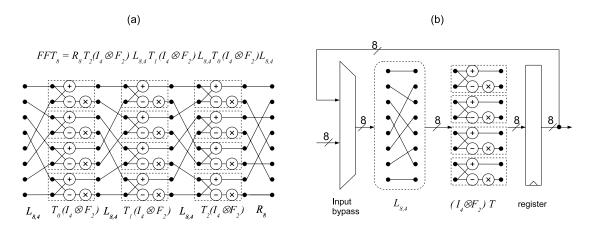

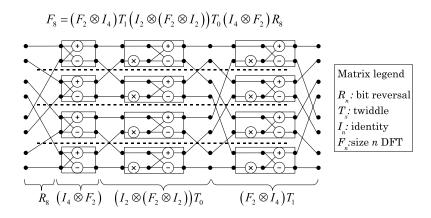

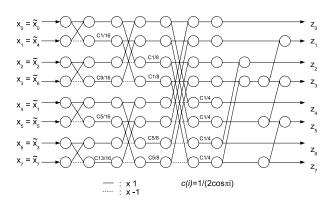

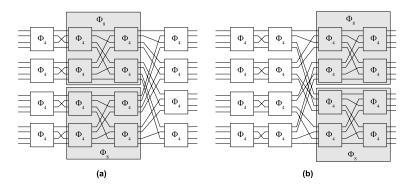

| 2-9    | (a)An 8-point Pease FFT formulation and dataflow graph. (b) full horizontal folding                                                                   | 33   |

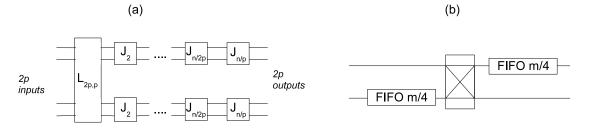

| 2–10   | (a)A vertically-folded $L_{n,n/2}$ permutation with $2p$ ports. (b) Detail of the $J_m$ component.                                                    | 34   |

| 3–1    | Sample topology.                                                                                                                                      | 39   |

| 3–2    | Block diagram of methodology.                                                                                                                         | 41   |

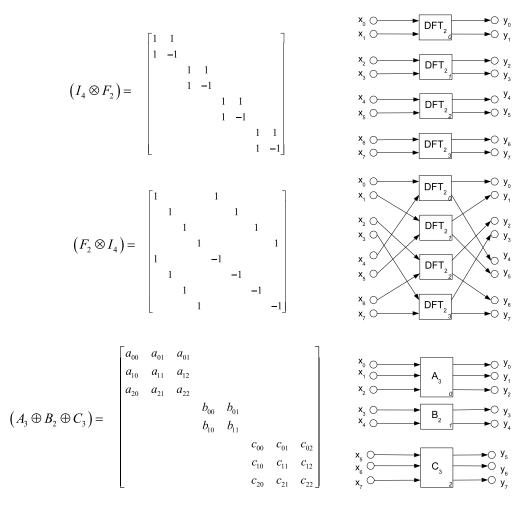

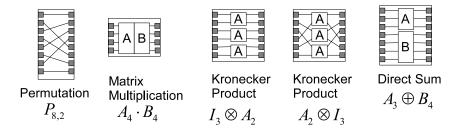

| 4–1    | Several KPA sparse matrices and their corresponding data order to-<br>pology DFGs                                                                     | 50   |

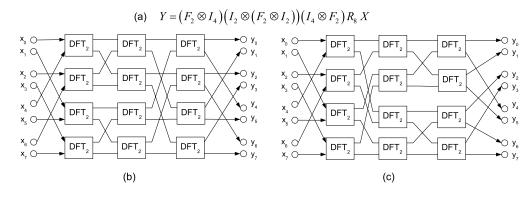

| 4 - 2  | KPA formulation and two isomorphic dataflow graphs.                                                                                                   | 51   |

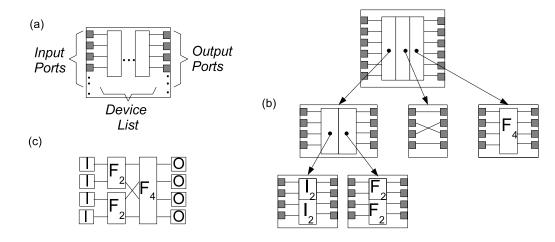

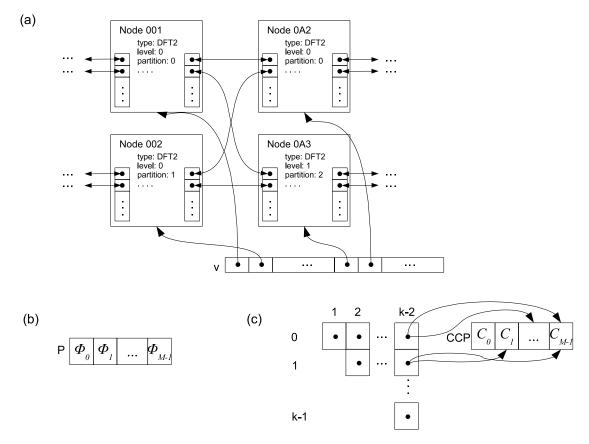

| 4–3    | (a) The KA-component data structure, (b) KA-component represen-<br>tation and (c) derived DFG for sample formulation $F_4P_{4,2}(I_2 \otimes F_2)$    | 51   |

| 4-4    | Common KPA operations and their KA-component representation                                                                                           | 52   |

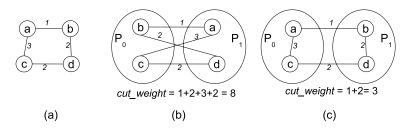

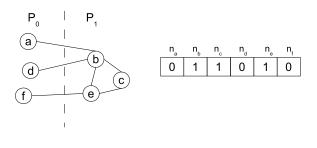

| 4–5    | (a) Graph (b) a partition solution, (c) partition solution after swapping nodes $a$ and $b$ .                                                         | 54   |

| 4–6 (a)Graph and (b)hypergraph representations of a circuit netlist 57 $$                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

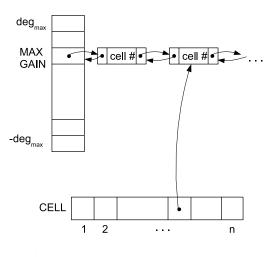

| 4–7 Bucket structure used in the Fiduccia-Mattheyses algorithm                                                                                                   |

| 4–8 Example of a chromosome encoding for a bipartitioning solution 61                                                                                            |

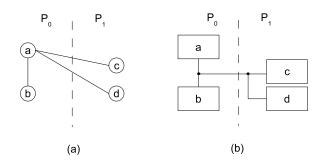

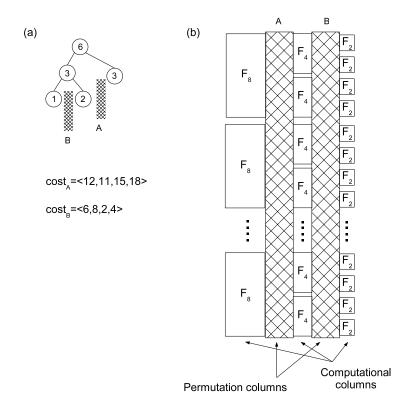

| 4–9 Effect of cut distribution on a DHA                                                                                                                          |

| 4–10 8-point DFT Cooley-Tukey formulation, showing initial linear hori-<br>zontal partition                                                                      |

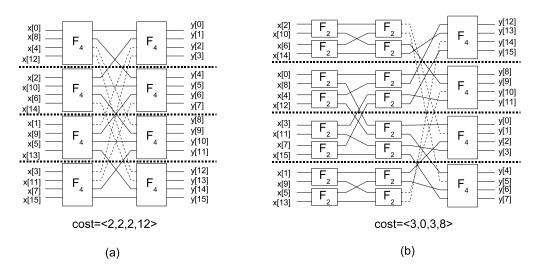

| 4–11 Two formulations for an 16-point FFT, representing different granu-<br>larities. Horizontal dashed lines represent the partition boundaries.                |

|                                                                                                                                                                  |

| 4–12 Device-level architectural model and block diagram for an FFT module. 76                                                                                    |

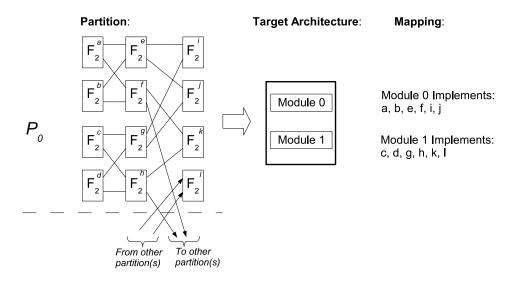

| 4–13 Example mapping of a DFG partition to a device with two architec-<br>tural modules                                                                          |

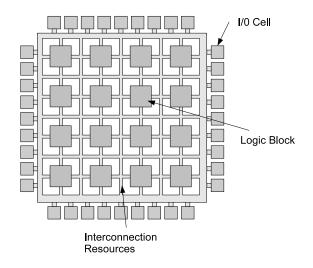

| 4–14 FPGA components                                                                                                                                             |

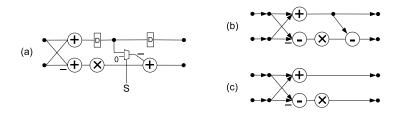

| 4–15 Functional primitive (a) implements the functionality of DFGs (b)<br>and (c)                                                                                |

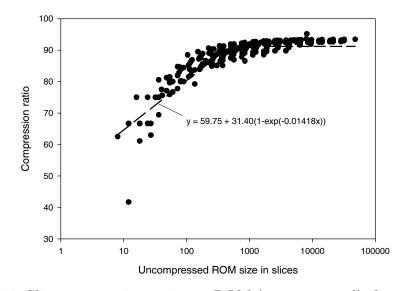

| 4–16 Slice compression ratio vs. ROM (uncompressed) slice utilization 85                                                                                         |

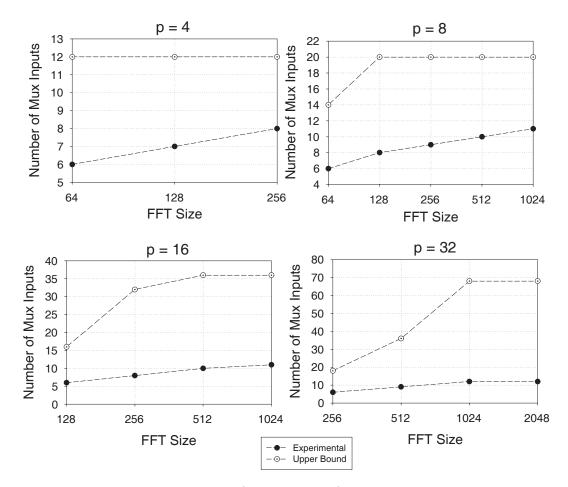

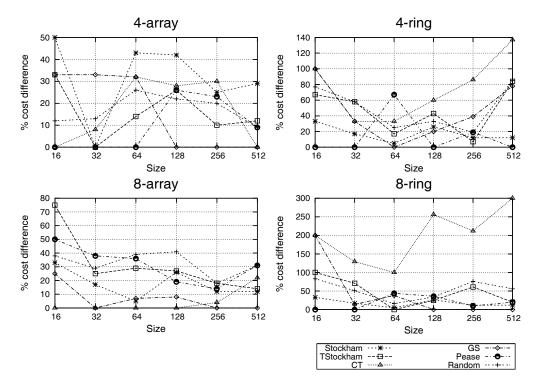

| 4–17 Experimental results for mapping of several FFT sizes to architectures<br>with 4, 8, 16, and 32 modules                                                     |

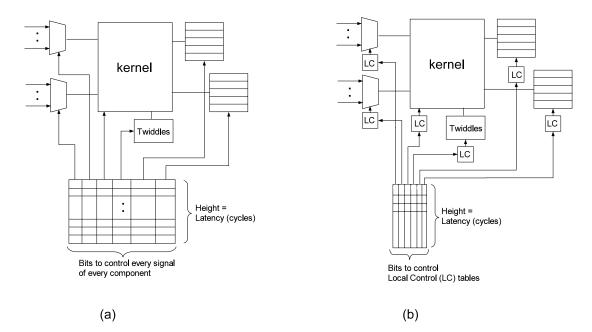

| 4–18 Two approaches for implementing module-level control logic (a)integrated,<br>(b)distributed                                                                 |

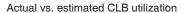

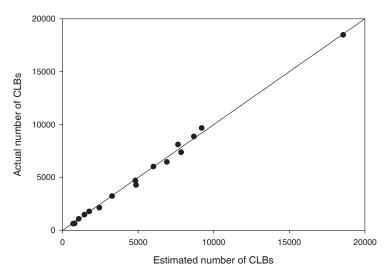

| 4–19 Actual vs. estimated slice utilization for various FFT sizes 92                                                                                             |

| 5–1 Results from the permutation experiment                                                                                                                      |

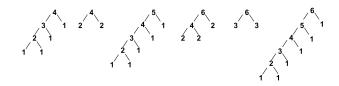

| 5–2 Two split trees for FFT size $n = 2^6$ and their formulations 100                                                                                            |

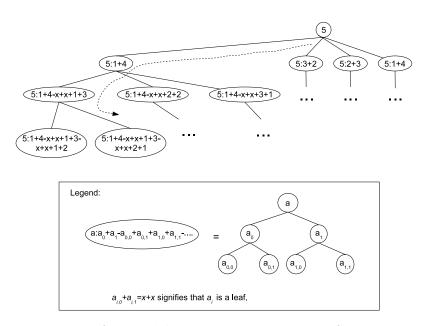

| 5–3 Part of a breakdown strategy mega-tree for 32-point FFT 102                                                                                                  |

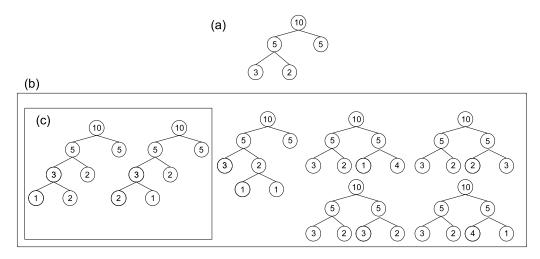

| 5–4 (a) A split tree for a 2 <sup>10</sup> -point FFT. (b) All possible children split trees of (a). (c) children split trees exclusively factoring leaf '3' 104 |

| 5–5 A split tree for a $n = 2^6$ -point DFT and part of its corresponding DFG.105                                                                                |

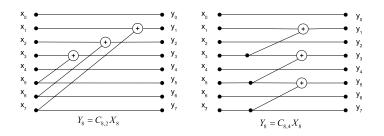

| 5–6 Dataflow graphs of $C_{8,2}$ and $C_{8,4}$ matrices                                                                                                          |

| 5–7 Practical split trees for 16, 32 and 64-point DCT when using Equation<br>5.6 for hardware implementation                                                     |

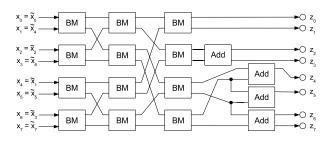

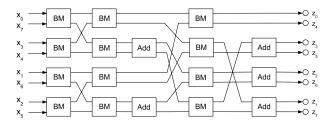

| 5–8 8-point HT-DCT data flow graph                                                                                                                               |

| 5–9 8-point HT-DCT using a single functional primitive that performs<br>both the BM and post-processing functionalities |

|-------------------------------------------------------------------------------------------------------------------------|

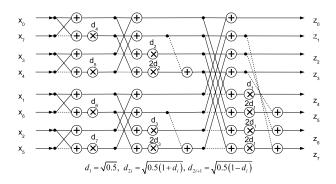

| 5–10 8-point SS-FCT                                                                                                     |

| 5–11 8-point SS-FCT using functional primitive blocks                                                                   |

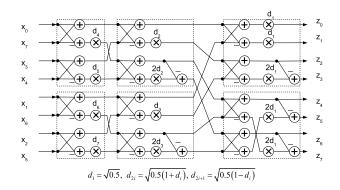

| 5–12 DFG for an 8-point NPS-DCT                                                                                         |

| 5–13 DFG for Equations 5.40 and 5.41                                                                                    |

| 5–14 Target topology for experiments                                                                                    |

| 6–1 Comparison of cost sum for initial horizontal partitions vs. random<br>for 4-Ring and 4-Array architectures         |

| 6–2 Comparison of iterations for initial horizontal partitions vs. random<br>for 4-Ring and 4-Array architectures       |

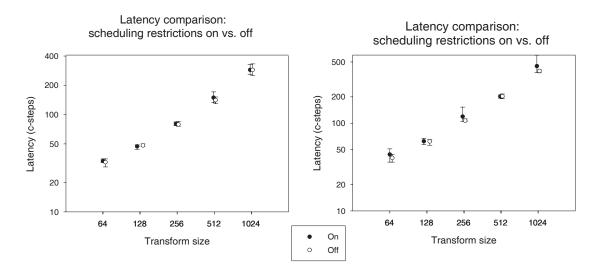

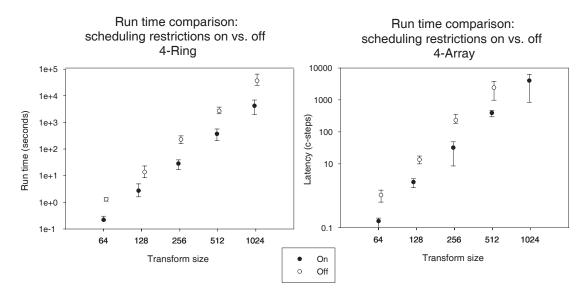

| 6–3 Comparison of latency with and without stage-restricted swaps 126 $$                                                |

| 6–4 Comparison of run time with and without stage-restricted swaps 126                                                  |

| A-1 Visualization of CT.fig using the Xfig program                                                                      |

| A-2 CT.gph file contents                                                                                                |

| A–3 Pseudocode for the KTG prototype implementation                                                                     |

| A–4 Illustration of the effect of KTG functions                                                                         |

| A-5 Extract of Eq_Node class                                                                                            |

| A-6 Extract of CComp, Port, and Device classes                                                                          |

| A-7 Extract of the Node class                                                                                           |

| A–8 Example of a topology description file                                                                              |

| A–9 Example of a device family resource file                                                                            |

| A–10Pseudocode for the DGP prototype implementation                                                                     |

| A–11Main DGP data structures                                                                                            |

| A–12Extract from DMAGIC's output                                                                                        |

| A–13Pseudocode for the DMAGIC prototype implementation                                                                  |

# LIST OF ABBREVIATIONS

| CAD                  | Computer Aided Design for VLSI Circuits      |

|----------------------|----------------------------------------------|

| DFG                  | Dataflow Graph                               |

| DHA                  | Distributed Hardware Architecture            |

| DST                  | Discrete Cosine Transform                    |

| DST                  | Discrete Signal Transform                    |

| EDA                  | Electronic Design Automation                 |

| FCCM                 | Field-Programmable Custom Computing Machines |

| FPGA                 | Field Programmable Gate Array                |

| $\operatorname{FFT}$ | Fast Fourier Transform                       |

| GPP                  | General Purpose Processor                    |

| HLS                  | High-Level Synthesis                         |

| KL                   | Kernighan-Lin                                |

| KPA                  | Kronecker Product Algebra                    |

| PDSP                 | Programmable Digital Signal Processors       |

| RTL                  | Register Transfer Level                      |

| SA                   | Simulated Annealing                          |

| VHDL                 | VHSIC Hardware Description Language          |

| VLSI                 | Very Large Scale Integration                 |

# CHAPTER 1

# Introduction

Applications for discrete signal transforms (DSTs), such as the Discrete Fourier Transform (DFT) and the Discrete Cosine Transform (DCT), abound in fields as diverse as communications, biomedical sciences, and astronomy. In these and many other fields, increases in the quantity and resolution of data and the need for faster processing, demand novel platforms and methodologies for the implementation of DSTs.

DSTs have been implemented to a myriad of computational platforms, from software-based General Purpose Processor systems to pure customized hardware such as Application Specific Integrated Circuits (ASICs). Throughout time, a cyclic behavior between software and hardware implementations has been observed [1] [2]. In the majority of cases, DST applications are initially implemented in software. Then, the need for real-time computation encourages their implementation to application-specific hardware. Meanwhile, advances in technology make the software implementation again competent. However, as this happens, applications evolve to demand more aggressive performance requirements, causing the cycle to repeat itself.

This observed trend highlights a major distinction between the software and hardware DST implementations: hardware implementations tend to achieve higher performance than software ones, but with a significant increase in the implementation effort. For example, it is a consistently observed fact that implementations of DSP applications in FPGAs can achieve 10x performance over their counterparts on Programmable Digital Signal Processors (PDSPs) [3]. Similarly, it is estimated that implementation effort for an FPGA is 5x-10x that of a PDSP. In today's world, where time to market can make the difference between a commercially successful product and a failure, it is common to see how implementers shy away from hardware implementations due to their steep development costs in time, cost, and hardware design expertise. To make these dedicated hardware implementations more widespread, we need, among other considerations, to improve the methods and tools used to design them.

Efficient mapping of algorithms to hardware is a challenging task. It demands a design philosophy somewhat dissimilar to programming a software-based system and imposes a number of additional difficulties. For instance, when implementing the functionality of an algorithm to hardware, in addition to deciding the type and order of operations, the designer must determine what functional units will be implemented in the device. This expands the range of possibilities available for the implementation of each algorithm, thus widening the solution space and the number of design options to be considered.

To aggravate the case against dedicated hardware implementations, some applications may require mapping to multiple devices (FPGAs or ASICs) to attain the degree of parallelism needed to achieve acceptable performance [4][5]. Today's developers not only have to think about the efficient hardware structures to implement their algorithms, but must also partition their designs into pieces that fit to each of the devices, and make effective use of the communications and memory resources provided in a multi-chip board. Clearly, to reduce the effort required for hardware implementations in multiple device architectures, the development of automatic algorithms for mapping and partitioning is essential. Correspondingly, there is a recently revived interest in dedicated hardware implementations using multiple intra-chip processing units, as in multi-core and System on Chip architectures, which can also benefit from effective partitioning schemes [6].

Several strategies have been proposed for automating the partitioning of algorithms to DHAs [7][8][9]. However most of the proposed automated mapping and partitioning methodologies are limited in at least one of two main aspects when used for DSTs. First, they perform optimizations at an abstraction level where it is difficult to detect functional features that could result in implementations with a higher performance. Second, they target general applications, so they only incorporate strategies that will work appropriately for the general case. Consequently, results from these strategies are often merely adequate in quality and require unnecessarily lengthened processes to converge to a solution.

DSTs represent a major energy, performance, and resource component in many modern applications, which merits the study of specialized methods for optimizing their implementation to modern computing platforms. The studies in this dissertation consider the development of a methodology for automated partitioning of discrete signal transforms to multiple-chip architectures. By targeting a specific group of algorithms we devised a partitioning methodology that exploits their functional features to attain better implementations in a more straightforward manner. The decision to focus on a certain class of algorithms allowed the incorporation of global algorithmic reformulations into the methodology, something that is not contemplated in existing methodologies.

#### 1.1 Objectives and Scope of Research

One of the main objectives of this research is to make a contribution to the software tools and general philosophy that designers encountering a partitioning task can have at their service. This was accomplished through the development of a partitioning methodology specifically designed for discrete signal transforms onto distributed hardware architectures. The developed methodology uses features and mathematical characteristics of discrete signal transforms, which would be lost or would incur in excessive effort if considered at lower abstraction levels. It encompasses several tasks that work together to accept DST algorithms, optimization objectives, constraints, and architectural specifications, and explores the solution space in search for an optimized implementation. Development of these tasks required the study, adaptation and creation of heuristic techniques to take advantage of improvement opportunities at the DST graph and formulation levels.

As a proof of concept to our methodology, its various stages were integrated into an automated tool. Individual components of the methodology were used to conduct experiments which, in turn, helped in defining the rest of the components. The integrated tool was used to partition DSTs to demonstrate its effectiveness and to compare its solutions with those of other published results. Outcomes from these evaluations confirmed the advantages of the considerations that were taken throughout the methodology's development. They validate our hypothesis that faster/higher-quality partitioning results can be obtained with a strategy that is aware of DST features.

#### 1.2 Dissertation Overview

The rest of the document is organized as follows. Chapter 2 provides a review of published work related to our topic, serving to sustain the importance of the problem, analyze what other researchers have accomplished, and to survey some areas of knowledge which influenced our solution. Chapter 3 formally states the problem of high-level partitioning of DSTs to DHAs and presents the main justification for our approach. This is followed by an overview of the approach followed in finding a solution to the stated problem.

Our partitioning methodology takes advantage of dataflow graph-level constructs while exploring alternative algorithmic DST formulations. Chapter 4 presents the development of processes to support graph-level exploration of a given DST formulation as well as the rationale behind their selection. This includes a Kronecker products algebra to DFG conversion tool, an extension of the Kernighan-Lin bipartitioning heuristic to k-way, and latency and hardware estimation strategies. Chapter 5 discusses how those tools were used to experiment with DST formulations and assess the effect of algorithmic level transformations. Observations from these experiments were used in the design of a formulation space exploration heuristic. The effectiveness of the various parts of our approach, as well as the unified methodology is validated in Chapter 6. Also in this chapter, results of the methodology are compared against those from a previous methodology. Chapter 7 reviews the main findings of this dissertation, highlighting the contributions of this work, and list several possible future research directions. The last chapter considers some of the ethical issues related to engineering research, in general, and to electronic design automation, in particular.

# CHAPTER 2

# **Related Work**

Our intended approach to the problem of partitioning of discrete signal transforms onto distributed hardware architectures requires combination of knowledge and techniques from at least three areas: electronic design automation, distributed hardware architectures, and digital signal processing. These three areas have been widely explored independently. Part of our proposed solution's novelty lies in finding how these areas of knowledge can complement each other to produce efficient hardware solutions for DST algorithms. This chapter reviews relevant technical literature to these areas, emphasizing the issues and techniques most closely related to the contributions of this dissertation.

The first section of this chapter provides a background on electronic design automation to establish the context in which automated partitioning methodologies are used. The second section reviews distributed hardware architectures and introduces the model we shall target throughout the development of our methodology. Section 2.3.2 discusses partitioning strategies for DHAs, with an emphasis on techniques at the behavioral level. The discussion highlights areas of opportunity with respect to our chosen problem and offers a glimpse into our proposed solution. Subsequently, in Section 2.4 we explore previous hardware implementations of a particular but representative signal transform, the discrete Fourier transform. Code generation methods that explore alternative DST formulations as part of their optimization strategy are reviewed in Section 2.5. Our main intention in these later sections is to project how previously developed hardware structures and algorithm techniques influenced our solution to the problem of automated partitioning of discrete signal transforms for distributed hardware architectures. Finally, Section 2.6 summarizes the main findings of our review of previous work.

#### 2.1 Electronic Design Automation

Designers looking for improved speed performance have always sought effective hardware implementations of digital signal processing applications [2]. It is commonly known that hardware implementations of these types of algorithms are faster than their software counterparts by orders of magnitude [3]. However, highperformance is achieved at an increased cost in technology price and implementation effort. Despite this, organizations seriously looking for increased performance are willing to pay the necessary price for technology. The biggest obstacle faced by designers in the process of successfully and efficiently mapping algorithms to hardware is how to handle the design complexity of these implementations. Typically, a team of designers is needed to build such project, consisting of experts in signal processing, algorithm design, and digital electronics. The required digital design expertise deters many signal processing enthusiasts and scientists from using hardware technology to test their algorithms, and achieving the promised high-performance. Clearly, an automated approach for mapping algorithms to hardware could open the opportunity of hardware implementation to the non-electronically inclined crowd and significantly ease solution exploration/optimization for digital designers.

The field of electronic design automation (EDA) has evolved to assist designers throughout the various tasks involved in the design and implementation of integrated circuits. From the highest to the lowest level of abstraction, elaborate tools have been developed to assist designers in the exploration and evaluation of the solution space to increase the odds of arriving at improved implementations. Figure 2–1 illustrates the traditional computer aided design flow for VLSI circuits (CAD) intended for a multi-device architecture. The process of transforming a digital system from a system specification into a hardware implementation is divided into four major steps: system-level synthesis, high-level synthesis, logic synthesis, and physical design, which are briefly discussed next.

Figure 2–1: Flow for Computer Aided Design for VLSI.

At the highest level of abstraction of the EDA process, a functional system description is provided using a high-level language. C, MATLAB and hardware description languages, such as VHDL and Verilog, have all been used for this purpose [10][11][12]. A process commonly referred to as *system-level synthesis* accepts this specification and outputs a partitioned set of tasks. Each partition is handled separately throughout the rest of the design flow and ultimately implemented on a particular target architecture device.

To accomplish the partitioning objectives, a system-level synthesizer starts by converting the human-specified algorithm formulation into an intermediate graphlike format that captures the control and data flow of the algorithm's operations. Graph representation schemes with various levels of granularity have been used for such representation. Among them, data flow graphs (DFGs) [8], control-data flow graphs (CDFGs) [13] and call graphs [14] are worth mentioning. The graph representation is then partitioned using implementation objectives such as performance, area, or power utilization.

*High-level synthesis* (HLS) transforms a behavioral description of the tasks that have been assigned to each device into a technology-independent structural description, such as a register transfer level (RTL) netlist. To accomplish this, HLS also represents the behavioral description in a graph-like format. This representation is then taken through a series of optimizing subtasks, namely allocation and scheduling [13][15]. During allocation, the hardware structures that will implement the systems' functionality (e.g. functional units) are determined. The aim of scheduling is to assign each of the algorithm's operations to a given time-step using the allocated units.

The last stages of the EDA flow convert the RTL-specified circuit onto a gate or transistor level netlist and determine the circuit layout description for the final implementation. In *logic synthesis* the RTL netlist is expanded into a gate-level circuit and optimized for a variety of objectives, such as area and delay. *Technology mapping* maps the gate-level circuit into the logic structures available in the targeted device. *Placement and routing* assign each of the technology-mapped circuit components a physical location on the target device and establish how circuit connections are physically routed through the device area. In the case of FPGAs, these steps are followed by the generation of a bitstream, which is used to program the reconfigurable elements in the device. For ASICS, the geometrical shapes that determine the various gates and connections are transcribed onto layout masks for fabrication.

Several computer aided design flows have been proposed to specifically target distributed hardware architectures [7][16][17]. All of them focus their attention on the partitioning step, either at the threshold between the system and high-level stages of the EDA process, as illustrated in Figure 2–1, or later after an RTL or logic design has been obtained. These strategies are oriented toward general algorithms and have not considered functional characteristics of signal transforms that we believe can conduct to a more straightforward exploration of the solution space. In the next sections we discuss distributed hardware architectures such as the ones we developed as part of this work. We also explain how the process of design automation, particularly at the system and high-level stages, is conducted for our architectures of interest.

#### 2.2 Distributed Hardware Architectures

DSP algorithms have been implemented to multiple computing platforms, seeking to take advantage of their cost/performance features. Our research focuses on architectures consisting exclusively of homogenous dedicated hardware, e.g. multi-FPGA boards. Throughout the rest of this document the term *distributed hardware architectures* will be used to refer to computational platforms consisting of multiple homogenous dedicated hardware devices, along with memory resources and some type of communication between the devices and memory.

Documentation of distributed hardware architectures using ASICs is scarce as this type of systems is commonly proprietary. However, a number of interesting variations of multiple FPGA systems have been constructed and documented since the early 1990s. The reconfigurable nature of these systems makes their documentation important for designers who are interested in implementing their own algorithms to these architectures. Even though we foresee that we will be targeting most of our implementation efforts to multiple-FPGA architectures, our proposed methodology for high-level partitioning is flexible enough to be useful for other architectures consisting of multiple dedicated hardware devices, such as traditional cell-based ASICs, and newer technologies like structured ASICs [18].

One of the first multiple-FPGA (MFPGA) systems to be documented was SPLASH [19]. It consisted of 32 Xilinx 3090 FPGAs with their corresponding 32 memory chips, connected in a linear array topology. A second version, SPLASH II improved on SPLASH by using higher capacity and faster FPGAs and providing a crossbar for one-hop data transfer for any two FPGAs as well as broadcast functionality [20]. Numerous DSP applications were mapped to SPLASH-2 with improvements in performance as compared to other implementation options [21][22][23]. Since then, a significant number of MFPGA systems have been constructed, both in Academia and Industry, each differing from the other in the number and types of FPGAs, the connection topology and memory capacity and arrangement [24][25]. Compton, et al., presented a thorough review of reconfigurable computer systems and issues, highlighting the fact that currently no consensus as to what combination of system characteristics, especially connection topology, are optimal for the general implementation of algorithms [26]. In spite of this, developers of these systems always seem to find a specific niche of benchmarks or metrics that make their systems superior to previous architectures.

The continued design of MFPGA systems for high performance signal processing applications evidences their acceptance as a preferred solution for low-volume or unique applications with a reasonable development time cycle. Two recent systems attest to this notion. The Serendip IV spectrometer, used as part of the Search for Extraterrestrial Intelligence (SETI) project, consists of 120 Xilinx FPGAs on 40 spectrum analyzer boards working in parallel to scan 168 million narrow-band (0.6 Hz) channels every 1.7 seconds [4]. Each SERENDIP IV board computes a four million point FFT by breaking the computation into three smaller FFTs (128, 128, and 256 points each). Each of the smaller transforms is implemented in a single FPGA. SERENDIP V, the next-generation of spectrometer boards, is being prepared for deployment. The majority of signal processing in this board is performed by a Xilinx XC2V6000 FPGA which can sustain a 64M-point FFT in real-time.

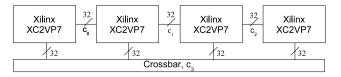

The Berkeley Emulation Engine (BEE) is an integrated rapid prototyping and design environment for communications and digital signal processing (DSP) systems, consisting of four multi-FPGA based processing units, each consisting of 4 processing and 1 interconnection FPGA [5]. Besides neighboring inter-FPGA connections, a novel hierarchical crossbar interconnection is used to support the communications among devices and boards. BEE2, a new version of BEE, is being justified by its designers not just as a hardware emulation platform but as a cost effective option to high performance computing [27].

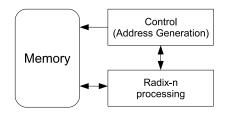

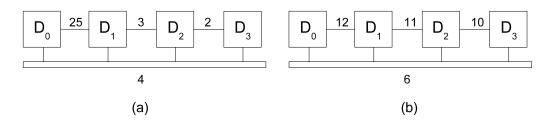

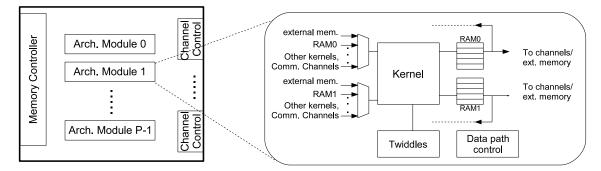

Figure 2–2 illustrates the general target architecture model of a DHA that will be used throughout the rest of our discussion. It consists of k dedicated hardware devices with local memory, connected in a ring or linear array topology with a crossbar serving as a global communication channel. This architecture is modeled after common multi-FPGA boards produced by vendors such as Annapolis (Wildforce) and Gidel (PROC20KE), as well as high-end academic reconfigurable systems such as the Berkeley Emulation Engine 2 (BEE2) [28]. Furthermore, this architecture can be considered scalable due to the number of connections per device and its topological symmetry.

Regardless of the increasing logic capacities foreseen for next generation FP-GAs and ASICs, there will always exist applications where distributed hardware systems will be either the only or the most cost/effective implementation option. Furthermore, using current manufacturing standards, single device yield diminishes dramatically as density and/or dye size are increased [29]. Power management and

Figure 2–2: General architectural model for a distributed hardware architecture.

heat dissipation also become prominent with increased density [30]. As illustrated in Figure 2–3 for Xilinx Virtex 2 FPGAs, these factors contribute to a cost/density ratio that increases with density. For these reasons, the development of novel methods for partitioning algorithms to multiple device systems will continue to be of great importance. In the next section we discuss partitioning/mapping strategies that have been proposed specifically targeting homogeneous distributed hardware architectures.

Figure 2–3: Price vs. capacity for Xilinx Virtex 2 FPGAs. Source: www.digikey.com

#### 2.3 Partitioning to DHAs

We begin our discussion of DHA partitioning methodologies with some general concepts about graph partitioning algorithms that are needed to understand the basic differences between the reviewed approaches. For purposes of discussion, specific graph partitioning heuristics, such as Kernighan-Lihn's and Fiduccia Matheysses, are discussed in Chapter 4, where they are analyzed as part of our design of a DST-influenced graph partitioning strategy.

#### 2.3.1 Graph partitioning algorithms

Partitioning algorithms can be classified as constructive or iterative. Constructive algorithms utilize clustering techniques to arrive at partitioning solutions. Each node initially belongs to its own cluster, and clusters are then gradually merged until a desirable partitioning is found. Thus, constructive algorithms follow a bottom-up greedy approach to partitioning.

Iterative algorithms, on the other hand, follow a top-down approach. They begin with an initial partition solution, which can be obtained in a naïve manner or from other partitioning strategies. At each iteration, the current solution is modified to obtain candidate solutions which are evaluated to determine their *goodness* according to the partitioning objectives. The *goodness* of a solution is quantified by combining the implementation objectives on an *objective function*<sup>1</sup>. The best candidate solution (or a randomly chosen one in the case of probabilistic algorithms) becomes the new current solution for the next iteration step.

Two main factors distinguish the various system-level iterative strategies that have been published in literature: the composition and evaluation of the objective

<sup>&</sup>lt;sup>1</sup> For example, the objective function of a partitioning process aimed at minimizing area and power utilization of an implementation could be as follows:  $F = k_1 \sum_i Area_i + k_2 \sum_i Power_i$  where *i* are the partitions, and  $k_1$  and  $k_2$  are weight coefficients (sums are assumed to be normalized).

function, and the mechanism used to guide the exploration of the solution space. During system-level partitioning, many of the desired objectives are related to lowerlevel implementation issues such as logic area, latency, and power utilization. The estimation of these properties from the high abstraction levels is not trivial, which explains why the development of fast and accurate estimators for those properties has been the topic of considerable research effort [7][13][31].

The graph min-cut bisection problem was demonstrated to be NP-complete by Garey [32]. All other size-constrained formulations of the graph partitioning problem are NP-complete too, as they reduce to the min-cut bisection problem [33]. Therefore, practical partitioning strategies rely on heuristics rather than on exact algorithms. Even though heuristic decisions cannot guarantee a good (or even a feasible) solution every time and under every situation, they represent a relatively fast and effective option for finding near-optimal solutions. Heuristic partitioning mechanism explore the solution space by using either deterministic or stochastic strategies. Deterministic techniques explore the solution space by applying rules that have been observed to lead to good solutions in practice. Two widely used heuristic partitioning techniques that employ a deterministic approach are Kernighan-Lin and Fiduccia-Matheyses. They are both considered greedy heuristics, accepting at each iterative step the best candidate solution. This makes them susceptible to local minimum solutions.

In an effort to avoid local minimum solutions, stochastic algorithms randomly select the solution for the next iteration, as is done in simulated annealing (SA), or build a new *generation* of solutions by crossing and mutating previous solutions, as in genetic algorithms (GA). Given the correct coding of the partitioning problem onto the probabilistic algorithm, a wise selection of solution exploration parameters (e.g. mutation probability in GA, cooling schedule in simulated annealing) and sufficient iterations, probabilistic algorithms can be relied on to find near-optimal partitioning solutions.

#### 2.3.2 Partitioning for Distributed Hardware Architectures

Previous strategies for partitioning algorithms onto homogeneous distributed hardware architectures can be classified into two categories, according to the general abstraction level at which partitioning is performed: partitioning at the RTL-orbelow-level, commonly referred to as *structural* partitioning, or partitioning at the behavioral-level, commonly known as *high-level* partitioning.

#### 2.3.3 Structural partitioning

Multi-FPGA logic emulation systems served as motivation for many of the reported structural partitioning methods. These platforms are used to verify the overall functionality of a logic implementation before committing it to a silicon solution, when software simulation techniques are impractical. Since silicon admits much denser structures than FPGAs, an array of these reconfigurable devices is used to implement the circuit under validation, thus requiring a mapping strategy.

Approaches to multi-chip partitioning at RTL-levels or below typically consist of enhancements and adaptations to well-known graph partitioning algorithms such as Kernighan-Lin and Fiduccia-Mattheyses. They tend to supplement a traditional graph partitioning algorithm with additional stages of optimization mechanisms. These mechanisms help the overall partitioning strategy comply with architecturespecific constraints or limitations, such as communication channels, I/O pins and logic resources, while guiding toward more effective partitioning solutions. Additionally, techniques such as unit/module cloning and communication channel multiplexing are integrated in an effort to solve the I/O limitation problem often seen in FPGA/ASIC implementations. The cutsize minimization objective stated in *strict* graph partitioning is enhanced by considering performance and cost issues, such as area, price, delay, and pin count. Frank M. Johannes gives a concise review of logic emulation structural partitioning methods in [34]. We discuss several representative methods to illustrate the salient issues in DHA structural partitioning.

The partitioning algorithms by Kim, Kuznar, and Chou had the objective of finding a *feasible* circuit partitioning solution while minimizing the monetary cost of an implementation; as measured by the cost of all DHA devices [35][36][37]. This objective somewhat departs from our intention in this thesis, since it assumes that the DHA can be custom-built using the results of the partitioning exploration, as opposed to targeting an established DHA platform, where device types and connections are predetermined. Nevertheless, they are representative of the types of strategies followed at the structural level.

Kuznar, et al. used Integer Linear Programming to determine the optimal distribution of Xilinx devices to partition a certain circuit in order to minimize price [35]. Then, a FM-based heuristic is recursively applied on the circuit to produce a subcircuit at each iteration that meets constraints determined by the previously determined target distribution.

Chou, et al. approached the circuit partitioning for huge logic emulation systems by using a hybrid algorithm that combined local bottom-up clustering and top-down recursive partitioning [36]. Partitioning was achieved by converting it to a Set Covering Problem and using the Espresso covering algorithm to improve results. Fang and Wu enhanced Chou's strategy by utilizing design hierarchy acquired from the circuit's pre-synthesis VHDL specification to guide clustering decisions [38]. This served to alleviate the I/O limitation problem typically encountered when partitioning to multiple FPGA platforms. Fang and Wu's work supports our general hypothesis of using higher-level information to provide better solutions to the multidevice partitioning problem. However, their approach is still essentially structural, which severely limits the amount of algorithmic information that they can use and makes their results highly dependent on programmer's style. Kim, et al. utilized a two-phased approach based on Fiduccia-Mattheyses [37]. The first stage iteratively improves an objective function that is the weighted sum of the cut size and the delay on the critical timing paths, while not considering system constraints such as routability. The second stage further optimizes the initial solution to satisfy the constraints. Results obtained with their method required less FPGAs, and obtained a lower monetary cost than the methods by Kuznar and Chou.

Scott Hauck devised a methodology to determine an order to map the results of recursive bipartitioning to the devices in a multi-FPGA board, based on the communication properties of the later [9]. His algorithm first determines the most congested DHA channel(s) using a technique developed by Yeh, et al. [39], and establishes the order in which the resulting partitions from a recursive Fiduccia-Matheyses bipartitioning should be assigned to the DHA devices. The most significant DHA connection topologies were analyzed and the resulting partition orderings were reported in his dissertation. However, no benchmark results using the complete methodology were found in literature.

In our opinion, most of the structural partitioning methodologies accomplish their main purpose, which is to effectively map a circuit to a set of devices for hardware emulation. Multi-FPGA logic emulation systems are not the end platform for the emulated designs, thus structural partitioning methodologies do not necessarily strive for implementation performance but rather compliance. They apply generalized optimization techniques based almost entirely on netlist information. We hypothesize that use of higher-level information is beneficial in partitioning strategies, especially when performance is an important implementation objective.

#### 2.3.4 Behavioral-level Partitioning

A commonly observed fact in EDA is that optimization methodologies that work at higher levels of abstraction usually achieve better performance than their lower level counterparts. Behavioral-level partitioners typically consist of a highlevel cost estimation mechanism coupled with a partitioning engine that relies on probabilistic or heuristic decisions to improve on the solution [7][8] [10][13]. A recurring characteristic of methodologies dealing with partitioning for homogenous distributed hardware architectures is that they integrate tasks that have been traditionally considered at the high-level synthesis stage, particularly allocation and scheduling. Thus, behavioral partitioning, rather than being a separate stage independent of high-level mapping synthesis tasks becomes an integrated partitioning/synthesis step.

The following three references represent, to the best of our knowledge, the best documented automated high-level partitioning strategies for DHAs. They exemplify the types of approaches that have been followed for the behavioral partitioning of general algorithms to DHAs, and highlight the combination of system-level and high-level issues throughout the optimization process:

Bringmann, et al. combined high-level synthesis and partitioning into a methodology aimed at multi-FPGA architectures [8]. They used a constructive (clustering) strategy to partition a flow-graph whose nodes represent arithmetic operations and whose edges represent data dependencies among the operations. The closeness metric used for clustering takes into consideration scheduling and allocation issues, such as the concurrency of operations (how probable it is for two operations to be executed in parallel) and the probability that an operation is on the critical path. Their algorithm is also capable of serializing data transfers among the devices in order to maximize circuit performance under the constraints of the target architecture. Their heuristic was used to partition four algorithms from the from the 1992 High-Level Synthesis Workshop [40], one of which was an 8-point DCT, to multi-FPGA platforms consisting of four Xilinx 4013 and 4025 devices.