#### **MICROCONTROLLER DESIGN AND CONCEPTS**

By

Victor L. Vargas Garcia

# A Project Report submitted in partial fulfillment of the requirements for the

#### degree of

#### MASTER OF SCIENCE in ELECTRIC ENGINEERING

# UNIVERSITY OF PUERTO RICO MAYAGUEZ CAMPUS

#### 2004

Approved by:

Fernando Vega, Ph.D. Graduate Committee Member

Jaime Arbona, Ph.D. Graduate Committee Member

Rogelio Palomera, Ph.D. Graduate Committee Advisor

Marco A. Arocha Ordoñez, Ph.D. Representative of Graduate Studies

J. Ortiz Alvarez, Ph.D. Chairperson of the Department

José A. Mari Mutt, Ph.D. Chairperson of Graduate Studies Date

Date

Date

Date

Date

Date

#### Abstract

### **Microcontroller Design and Concepts**

By

#### Victor L. Vargas Garcia

A method for microcontroller design was developed. A basic data path configuration capable of processing the microcontroller basic instruction set was developed first. Based on this configuration, a four-bit microcontroller was developed from its most basic instruction set to the most complex one.

Through the design process, the microcontroller hardware evolves into a complex one as more instructions are added to the basic instruction set. More hardware is added in parallel to the basic data path configuration to make the execution of more complex instructions possible.

As a result it is expected that readers become familiar with the fundamental microcontroller concepts and operations. Design steps, implementation and testing of all the microcontroller development circuits are shown graphically and explained in detail. Finally designers will have a basic guide to develop their own microcontroller using this work procedure.

#### **COMPENDIO**

#### **Microcontroller Design and Concepts**

By

#### Victor L. Vargas García

Un método para el diseño de microcontroladores fue desarrollado partiendo de una configuración básica para el camino de datos que permite la ejecución del grupo más sencillo de instrucciones para un microcontrolador. Usando ésta configuración básica, un microcontrolador de 4 bits fue desarrollado desde sus instrucciones más básicas hasta las más complejas.

A medida que el proceso de desarrollo y evolución del microcontrolador se lleva a cabo, instrucciones más complejas se van sumando al conjunto de instrucciones básicas del microcontrolador, añadiendo circuitos en paralelo al circuito básico que forma el camino de datos que permiten que éstas nuevas instrucciones se puedan ejecutar.

Como resultado el lector tendrá una guia y una idea más clara sobre los fundamentos básicos de los microcontroladores, su funcionamiento y su arquitectura. Se mostrarán de una manera grafica y explicada en detalle, los pasos de diseño, implementación y prueba de los circuitos usados en el desarrollo de microcontroladores. Finalmente los diseñadores tendrán una guia básica para desarrollar su propio microncontrolador usando el procedimiento descrito en este trabajo. To my Lord, my family and all my friends, for all the love and support. Without any of you this work would not have been possible.

To Dr. Rogelio Palomera, who has been not only an excellent professor, but more important, he has been a good friend.

#### Acknowledgements

Special thanks to Dr. Rogelio Palomera García for being my advisor, for his helpful comments, guidance and suggestions and above all, for being patient and good friend. To my parents Hector Vargas and Zenaida García for their unconditional support and help. To Mirelly Castro for being an excellent friend and for her support in difficult times.

Thanks to Dr. Jaime Arbona for his advice and valuable knowledge in electrical engineering. Thanks to Jorge Justiniano Magraner and Hector Santos for their patience, time and for being great persons and good friends.

# **Table of Contents**

|       | Tables<br>Figures                                | ix<br>xi |

|-------|--------------------------------------------------|----------|

|       |                                                  |          |

| 1     | Introduction.                                    | 1        |

| 1.1   | Justification                                    | 1        |

| 1.2   | Research Objectives                              | 5        |

| 1.3   | Simulations.                                     | 5        |

| 1.4   | Work Organization                                | 6        |

|       |                                                  |          |

| 2     | Theory and Applications.                         | 7        |

| 2.1   | Microcontroller Aplications                      | 7        |

| 2.2   | The Processor and the Microntroller Concepts.    | 7        |

| 2.3   | Microcontroller Performance Factors              | 9        |

| 2.4   | The General Purpose Microcontroller.             | 10       |

| 2.5   | Comparing Microcontrollers and Microprocessors   | 11       |

|       |                                                  |          |

| 3     | The Microcontroller Implementation and Operation | 13       |

| 3.1   | Logic Circuit Implementation Alternatives        | 13       |

| 3.2   | Hardware Description Languages (HDLs)            | 17       |

| 3.3   | Trade offs in Microcontroller Design.            | 18       |

| 3.4   | The Microcontroller Programming                  | 19       |

| 3.5   | The Microcontroller Operation                    | 20       |

| 3.5.1 | The Program Counter                              | 21       |

| 3.6   | Flags.                                           | 21       |

| 4   | The Microcontroller Design Steps | 22 |

|-----|----------------------------------|----|

| 4.1 | Methodology Steps                | 22 |

| 4.2 | Steps Description.               | 23 |

| 5     | The Microcontroller Design Example.                            | 32 |

|-------|----------------------------------------------------------------|----|

| 5.1   | STEP I and II The Microcontroller Justification and operations | 32 |

| 5.2   | STEP III The instruction Set                                   | 32 |

| 5.3   | STEP IV The Microcontroller Architecture Definition            | 34 |

| 5.4   | STEP V The Arithmetic Logic Unit                               | 37 |

| 5.4.1 | The Adder and the Subtractor                                   | 38 |

| 5.4.2 | Logical Bit Wise Operations                                    | 40 |

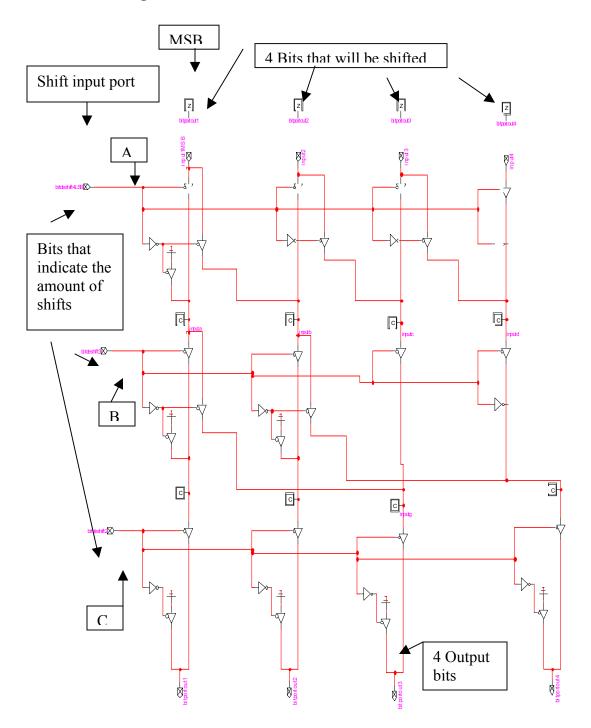

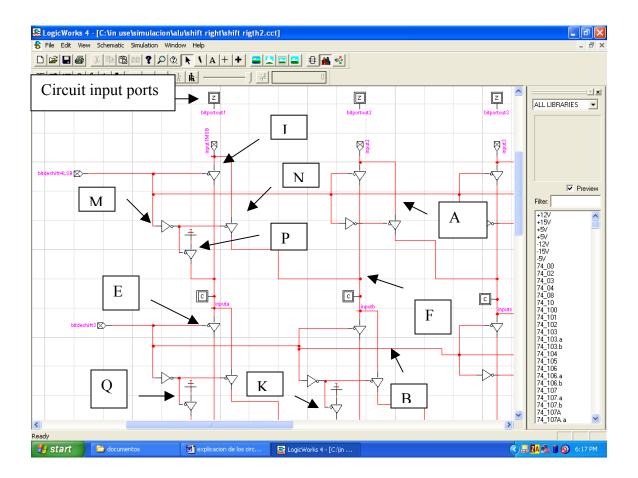

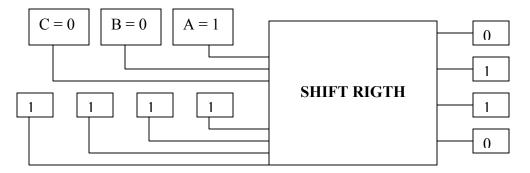

| 5.4.3 | Shift Right                                                    | 42 |

| 5.4.4 | Arithmetic Shift                                               | 45 |

| 5.4.5 | Circular Shift                                                 | 46 |

| 5.4.6 | Shift Left                                                     | 48 |

| 5.4.7 | Arithmetic Logic Unit Final Implementation                     | 49 |

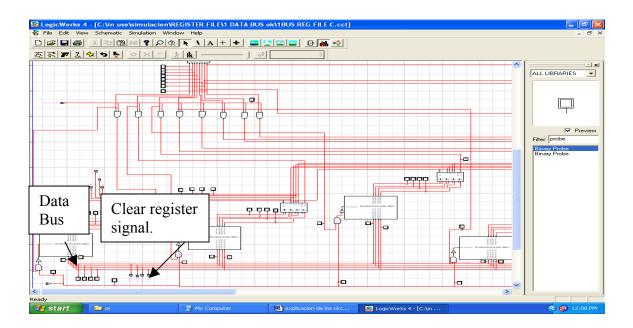

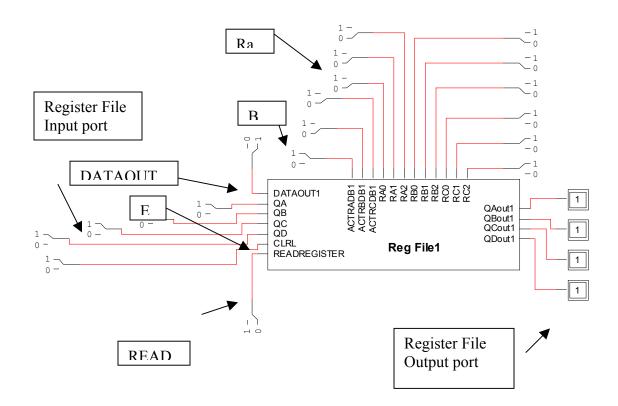

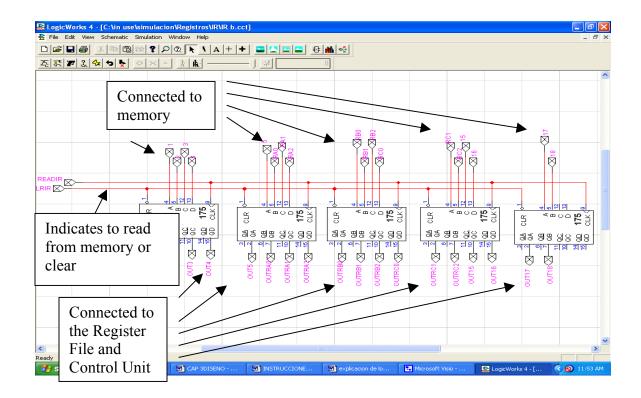

| 5.5   | STEP VI The Register File                                      | 54 |

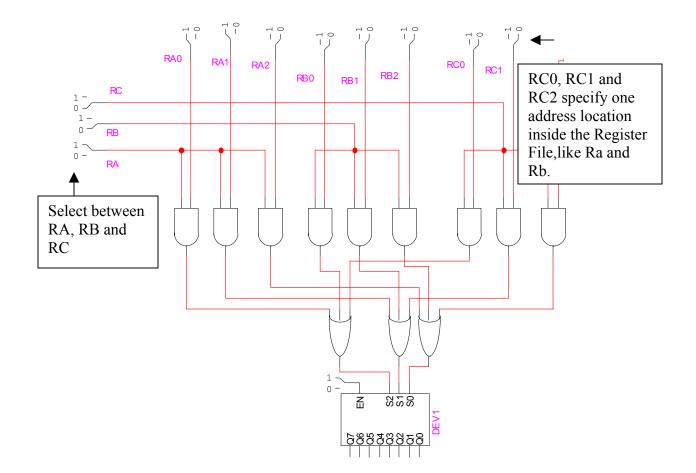

| 5.5.1 | The Register File Selection Stage                              | 54 |

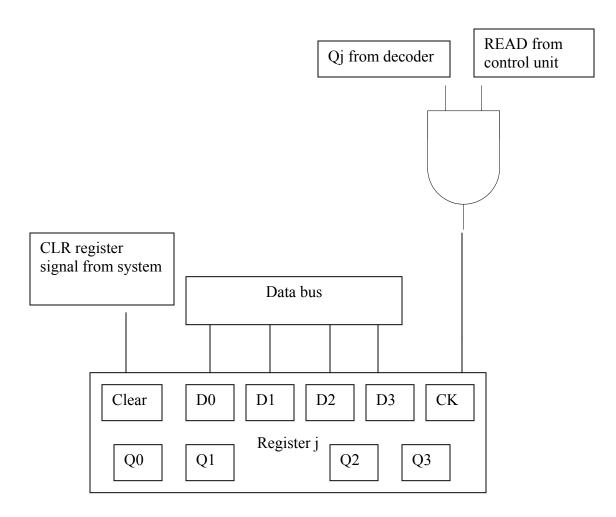

| 5.5.2 | The Register File Input Stage                                  | 56 |

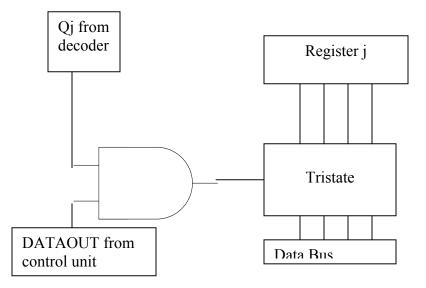

| 5.5.3 | The Register File Output Stage                                 | 57 |

| 5.5.4 | The Register File Implementation                               | 58 |

| 5.6                                                                   | STEP VII The Instruction Register.                                                                                                               | 59                            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

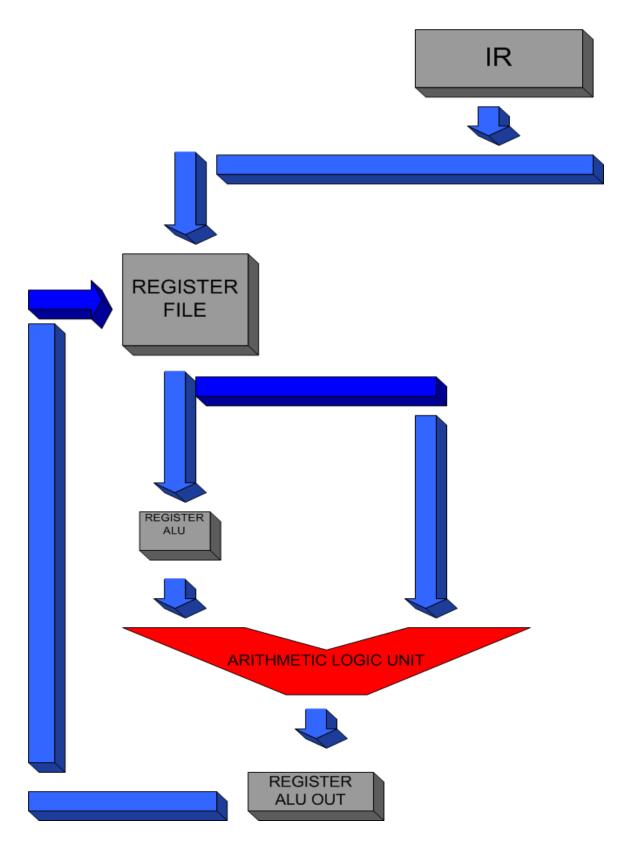

| 5.7                                                                   | STEP VIII The Data Path.                                                                                                                         | 60                            |

| 5.7.1                                                                 | The Basic Data Path                                                                                                                              | 60                            |

| 5.7.2                                                                 | Data Path With Immediate Operations                                                                                                              | 62                            |

| 5.7.3                                                                 | Shift Operations                                                                                                                                 | 65                            |

| 5.8                                                                   | STEP IX The PC, jump and Data Transfer Instructions                                                                                              | 70                            |

| 5.8.1                                                                 | The Branch Instruction                                                                                                                           | 70                            |

| 5.8.2                                                                 | The Program Counter                                                                                                                              | 72                            |

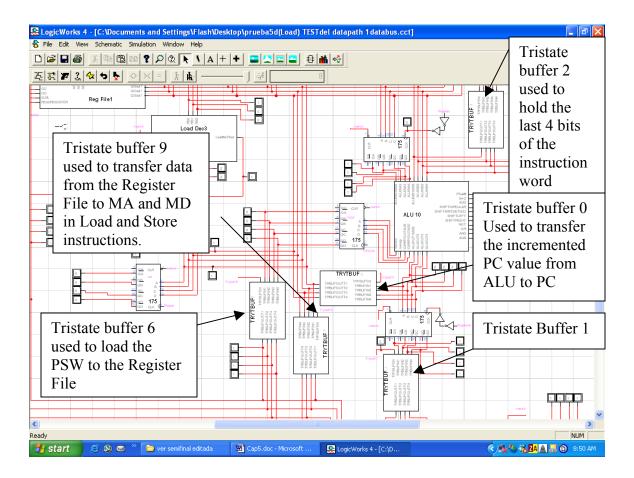

| 5.8.3                                                                 | Load and Store operations                                                                                                                        | 76                            |

| 5.8.4                                                                 | Miscellaneous Operations                                                                                                                         | 81                            |

|                                                                       |                                                                                                                                                  |                               |

| 6                                                                     | STEP X The Control Unit.                                                                                                                         | 156                           |

| <b>6</b><br>6.1                                                       | STEP X The Control Unit.                                                                                                                         | <b>156</b><br>84              |

|                                                                       |                                                                                                                                                  |                               |

| 6.1                                                                   | The Fetch Process                                                                                                                                | 84                            |

| 6.1<br>6.2                                                            | The Fetch Process                                                                                                                                | 84<br>88                      |

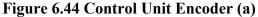

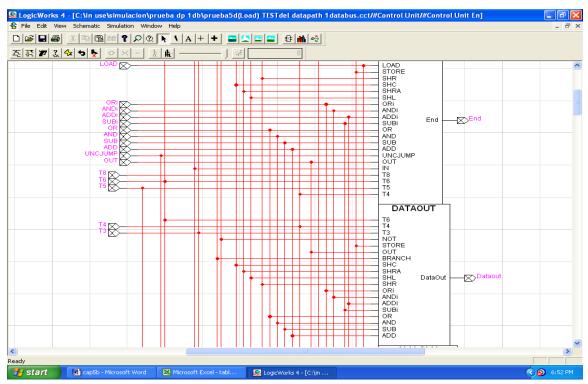

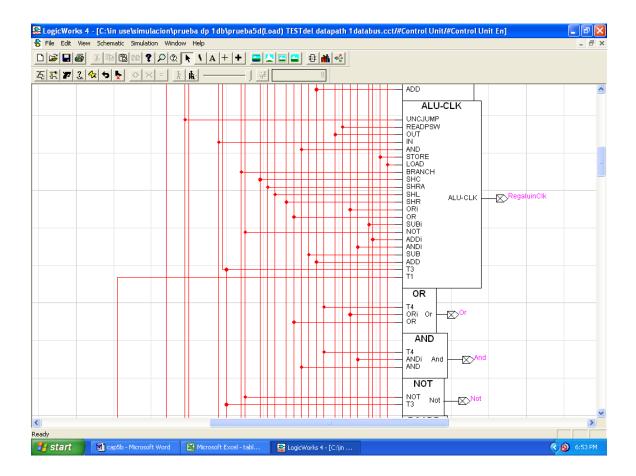

| 6.1<br>6.2<br>6.3                                                     | The Fetch Process<br>The Control Unit Encoder<br>The Control Unit Operational Code Decoder                                                       | 84<br>88<br>142               |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>             | The Fetch Process<br>The Control Unit Encoder<br>The Control Unit Operational Code Decoder<br>The Control Unit Timer                             | 84<br>88<br>142<br>146<br>148 |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | The Fetch Process<br>The Control Unit Encoder<br>The Control Unit Operational Code Decoder<br>The Control Unit Timer<br>Implementation Problems. | 84<br>88<br>142<br>146        |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | The Fetch Process<br>The Control Unit Encoder<br>The Control Unit Operational Code Decoder<br>The Control Unit Timer<br>Implementation Problems. | 84<br>88<br>142<br>146<br>148 |

### List of Tables

| 4.1  | Methodology Steps                                                        | 22 |

|------|--------------------------------------------------------------------------|----|

| 5.1  | The Microcontroller Instruction Set                                      | 32 |

| 5.2  | The Conditional Logic Cases                                              | 72 |

| 6.1  | Add instruction signal activation by clock cycle                         | 89 |

| 6.2  | Sub instruction signal activation by clock cycle                         | 89 |

| 6.3  | AND instruction signal activation by clock cycle                         | 90 |

| 6.4  | Or instruction signal activation by clock cycle                          | 90 |

| 6.5  | ADDi instruction signal activation by clock cycle                        | 91 |

| 6.6  | Subi instruction signal activation by clock cycle                        | 91 |

| 6.7  | ANDi instruction signal activation by clock cycle                        | 92 |

| 6.8  | Ori instruction signal activation by clock cycle                         | 92 |

| 6.9  | Not instruction signal activation by clock cycle                         | 93 |

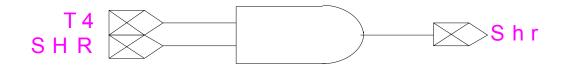

| 6.10 | SHR instruction signal activation by clock cycle                         | 93 |

| 6.11 | SHRA instruction signal activation by clock cycle                        | 94 |

| 6.12 | SHC instruction signal activation by clock cycle                         | 94 |

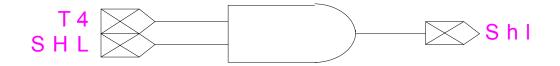

| 6.13 | SHL instruction signal activation by clock cycle                         | 95 |

| 6.14 | BRANCH instruction signal activation by clock cycle                      | 95 |

| 6.15 | LOAD instruction signal activation by clock cycle                        | 96 |

| 6.16 | STORE instruction signal activation by clock cycle                       | 96 |

| 6.17 | IN instruction signal activation by clock cycle                          | 97 |

| 6.18 | OUT instruction signal activation by clock cycle                         | 97 |

| 6.19 | READ PSW instruction signal activation by clock cycle                    | 98 |

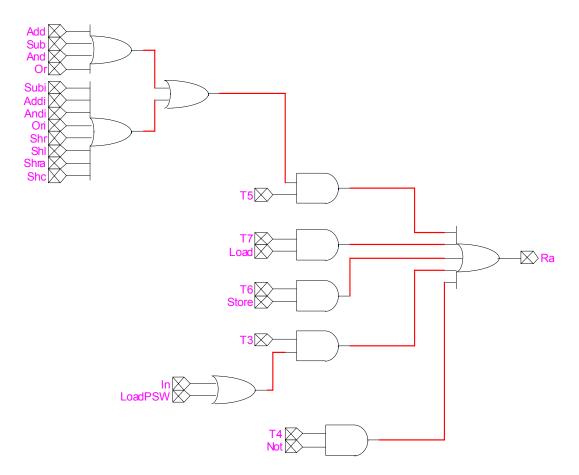

| 6.20 | Ra signal activation in terms of instructions and cycles                 | 99 |

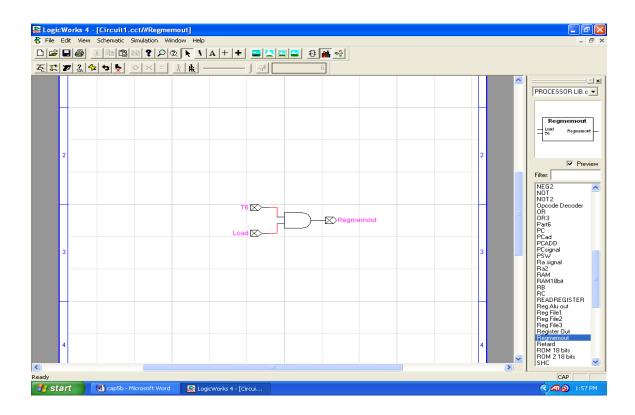

| 6.21 | Regmemout signal activation in terms of instructions and cycles          | 10 |

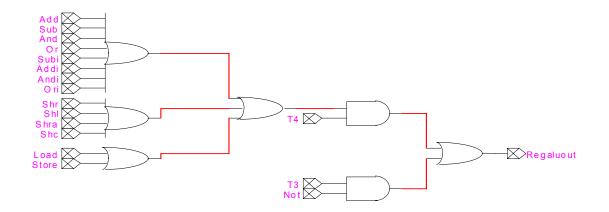

| 6.22 | Reg Alu out signal activation in terms of instructions and cycles        | 10 |

| 6.23 | Try state buffer 0 signal activation in terms of instructions and cycles | 10 |

| 6.24 | Try state buffer 1-signal activation in terms of instructions and cycles | 10 |

| 6.25 | Try state buffer 2-signal activation in terms of instructions and cycles | 10 |

| 6.26 | Data out signal activation in terms of instructions and cycles           | 10 |

| 6.27 | Reg Alu in signal activation in terms of instructions and cycles         | 11 |

| 6.28 | Rb signal activation in terms of instructions and cycles                 | 11 |

| 6.29 | Rc signal activation in terms of instructions and cycles                 | 11 |

| 6.30 | Read register signal activation in terms of instructions and cycles      | 11 |

| 6.31 | PC signal activation in terms of instructions and cycles                 | 117 |

|------|--------------------------------------------------------------------------|-----|

| 6.32 | END signal activation in terms of instructions and cycles                | 119 |

| 6.33 | Regaluin signal activation in terms of instructions and cycles           | 130 |

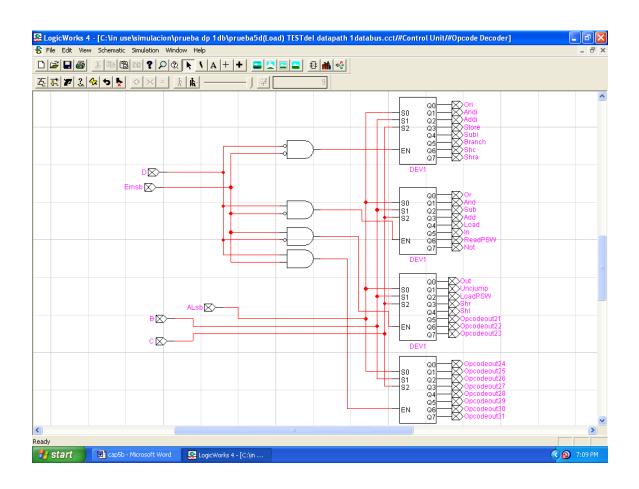

| 6.34 | The Opcode Decoder truth table                                           | 147 |

| 7.1  | Add instruction signal activation verbal descriptions.                   | 151 |

| 7.2  | AND instruction signal activation verbal descriptions                    | 153 |

| 7.3  | Arithmetic Shift Right instruction signal activation verbal descriptions | 155 |

| 7.4  | Branch (conditional) signal activation verbal descriptions               | 156 |

| 7.5  | Branch (unconditional) signal activation verbal descriptions             | 157 |

| 7.6  | Circular Shift instruction signal activation verbal descriptions         | 159 |

| 7.7  | IN instruction signal activation verbal descriptions                     | 160 |

| 7.8  | Immediate Addition instruction signal activation verbal descriptions     | 162 |

| 7.9  | Immediate AND instruction signal activation verbal descriptions          | 164 |

| 7.10 | Immediate OR instruction signal activation verbal descriptions           | 166 |

| 7.11 | Immediate Subtraction instruction signal activation verbal descriptions  | 168 |

| 7.12 | Load instruction signal activation verbal descriptions                   | 170 |

| 7.13 | NOT instruction signal activation verbal descriptions                    | 172 |

| 7.14 | Immediate OR instruction signal activation verbal descriptions           | 174 |

| 7.15 | Out instruction signal activation verbal descriptions.                   | 175 |

| 7.16 | READ PSW instruction signal activation by clock cycle                    | 176 |

| 7.17 | Shift Left instruction signal activation verbal descriptions             | 178 |

| 7.18 | Shift Right instruction signal activation verbal descriptions.           | 180 |

| 7.19 | Store instruction signal activation verbal descriptions                  | 182 |

| 7.20 | Subtraction instruction signal activation verbal descriptions            | 184 |

## List of Figures

| 2.1  | The Microprocessor Configuration                    | 11 |

|------|-----------------------------------------------------|----|

| 2.2  | The Microcontroller Configuration                   | 12 |

| 3.1  | Microcontroller Implementation Alternatives         | 14 |

| 5.1  | The Instruction Format                              | 35 |

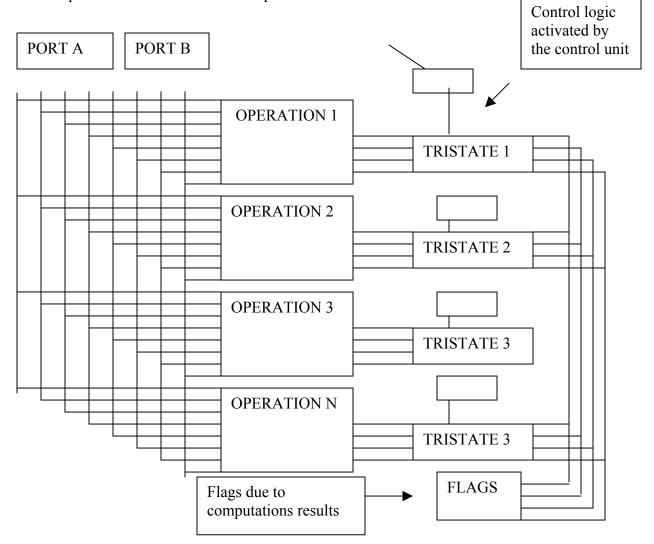

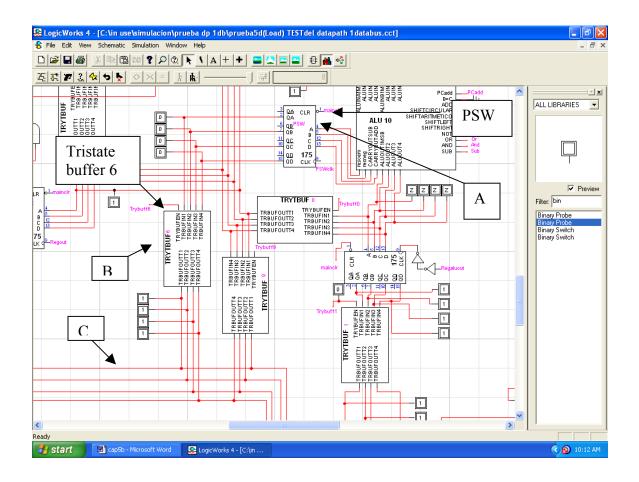

| 5.2  | The Arithmetic Logic Unit Structure                 | 37 |

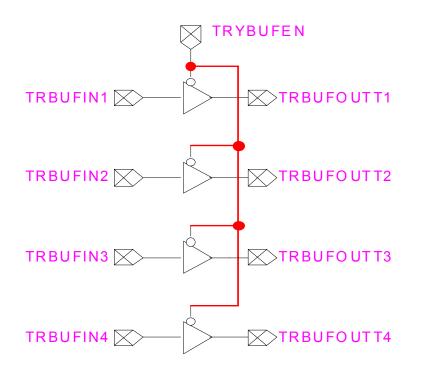

| 5.3  | The Tristate Buffer Implementation Circuit          | 38 |

| 5.4  | The Adder Example                                   | 39 |

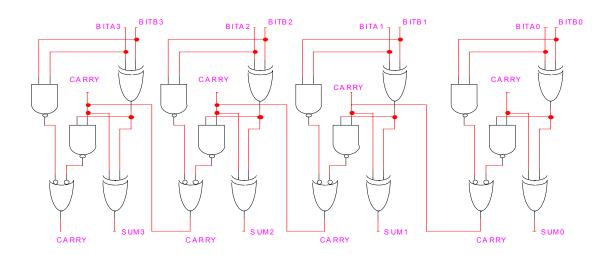

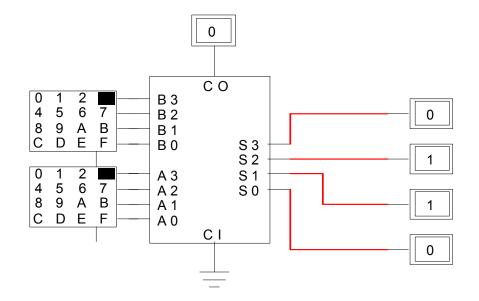

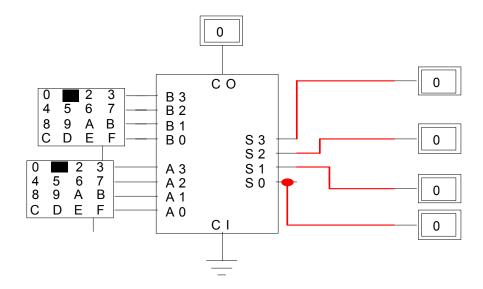

| 5.5  | Example of Adder Circuit Testing                    | 39 |

| 5.6  | The Subtractor Circuit Implementation               | 40 |

| 5.7  | AND Circuit Implementation                          | 41 |

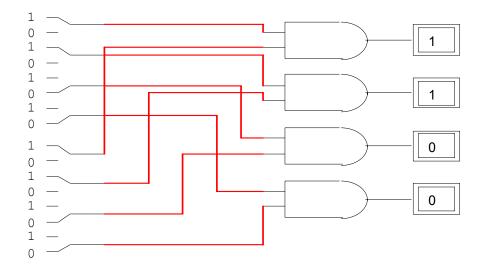

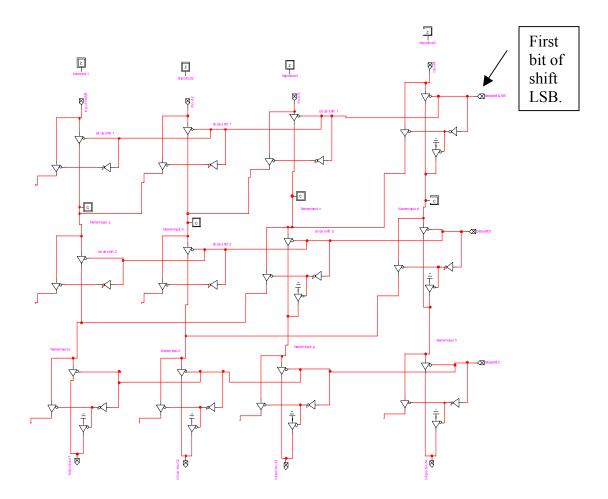

| 5.8  | The Shift Right Implementation Circuit              | 42 |

| 5.9  | The Shift Right Instruction Mechanism               | 43 |

| 5.10 | The Shift Right Circuit Testing: Shifting 1100 once | 44 |

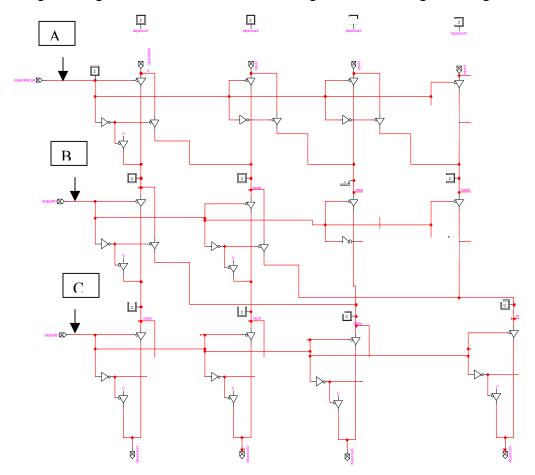

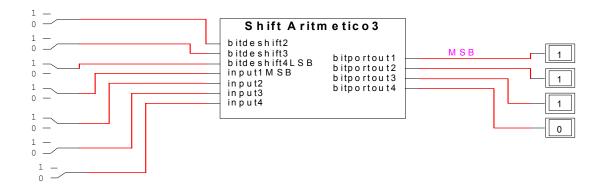

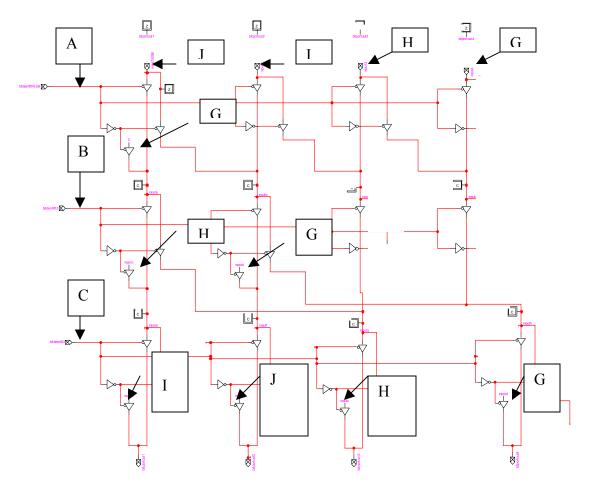

| 5.11 | The Arithmetic Shift Implementation Circuit.        | 45 |

| 5.12 | The Arithmetic Shift Circuit Testing                | 46 |

| 5.13 | Circular Shift Circuit Implementation               | 47 |

| 5.14 | Shift Left Implementation Circuit                   | 48 |

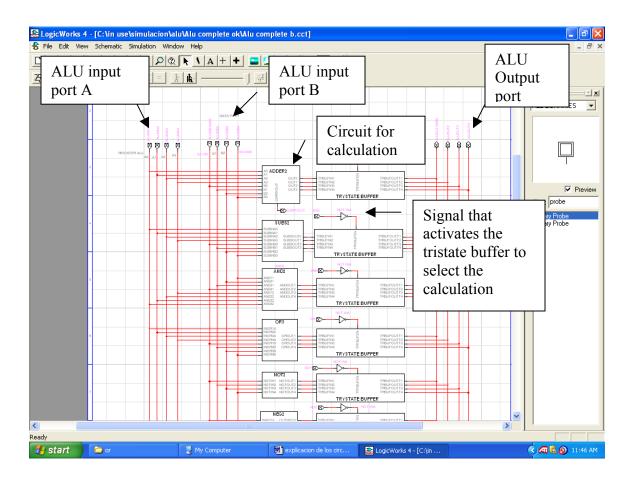

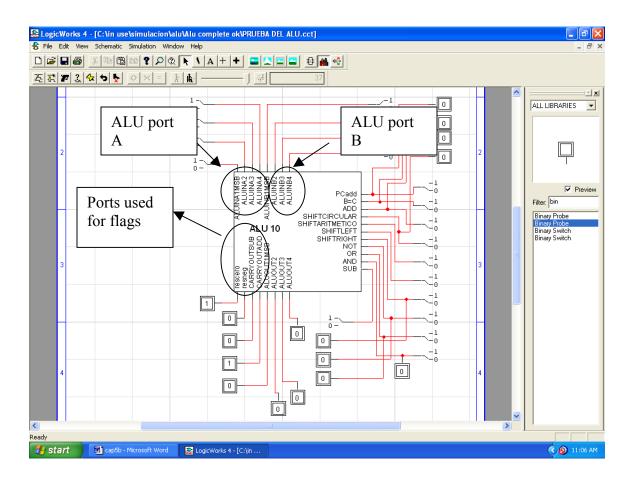

| 5.15 | The ALU Implementation (top view)                   | 50 |

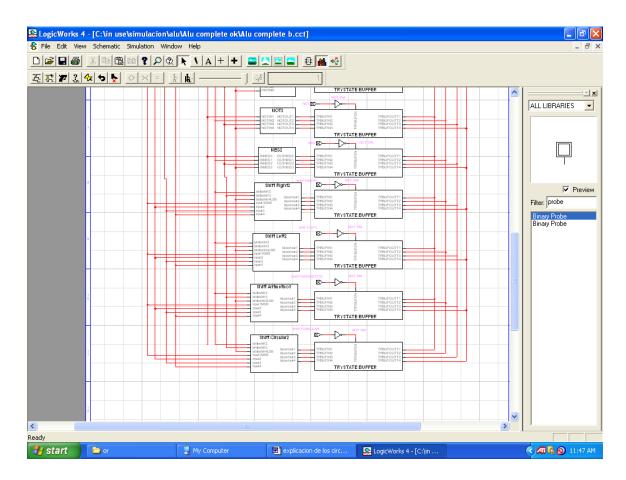

| 5.16 | The ALU Implementation (bottom view)                | 51 |

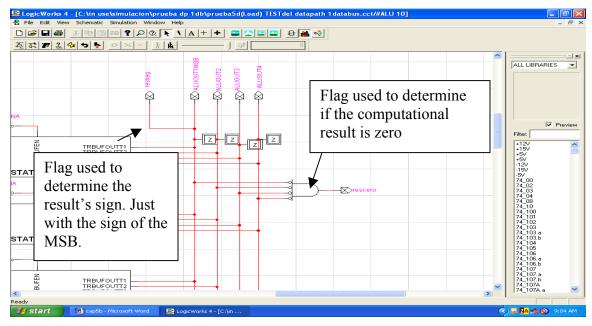

| 5.17 | The ALU Flags Hardware                              | 51 |

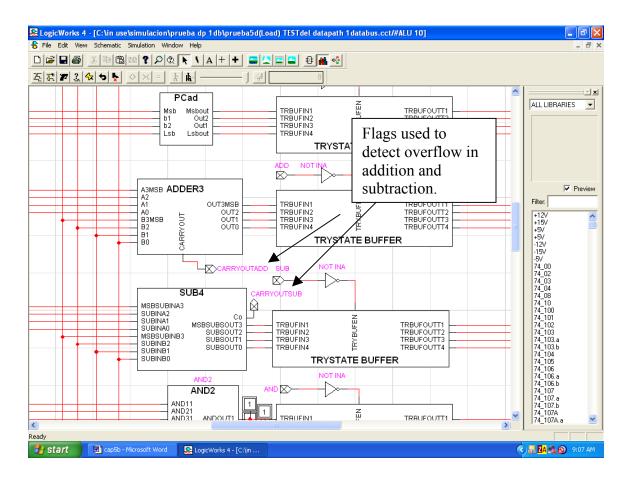

| 5.18 | Flags Used for Overflow                             | 52 |

| 5.19 | The ALU Testing (top view)                          | 53 |

| 5.20 | The Register File Selection Stage                   | 55 |

| 5.21 | Module Rj of the Register File: Input Stage         | 56 |

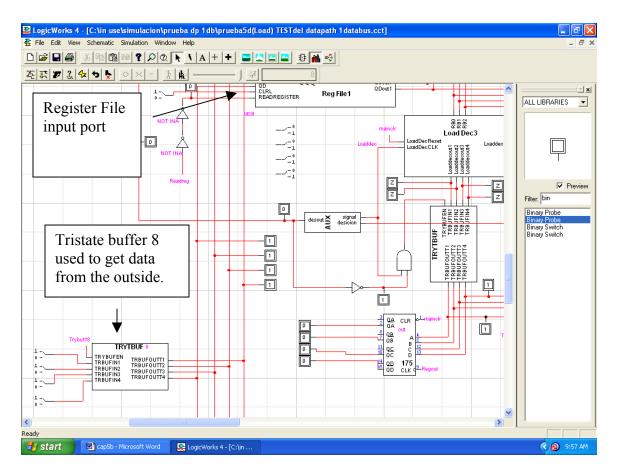

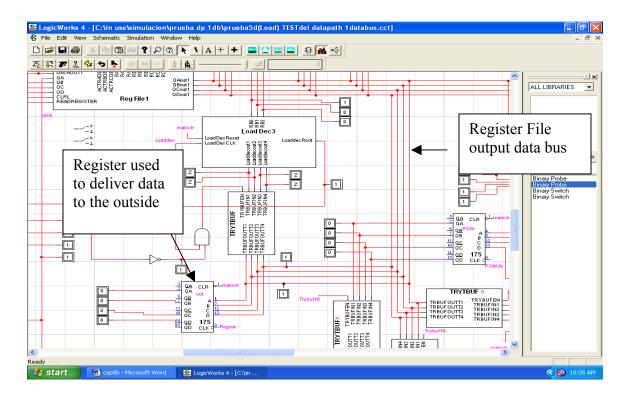

| 5.22 | Module Rj of the Register File: Output Stage        | 57 |

| 5.23 | The Register File Input Stage                       | 57 |

| 5.24 | The Register File Testing                           | 58 |

| 5.25 | The Instruction Register Implementation             | 59 |

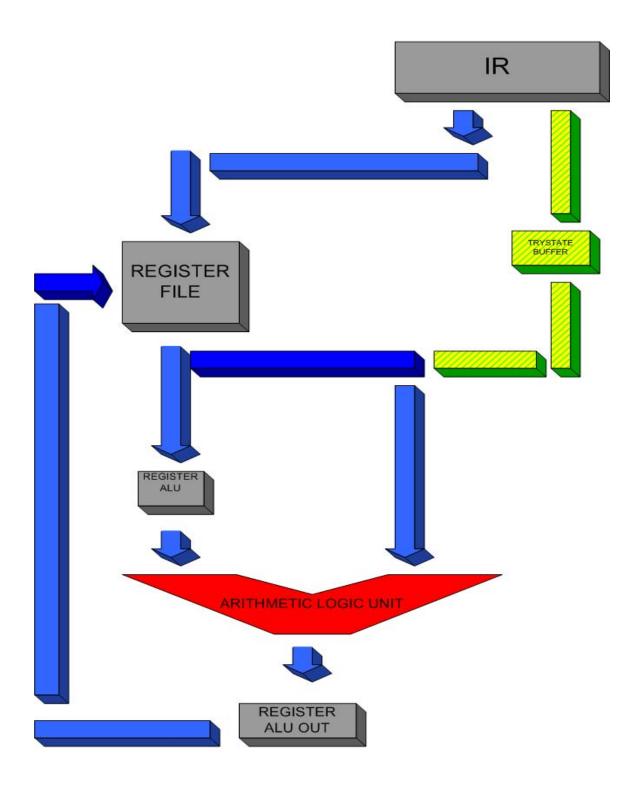

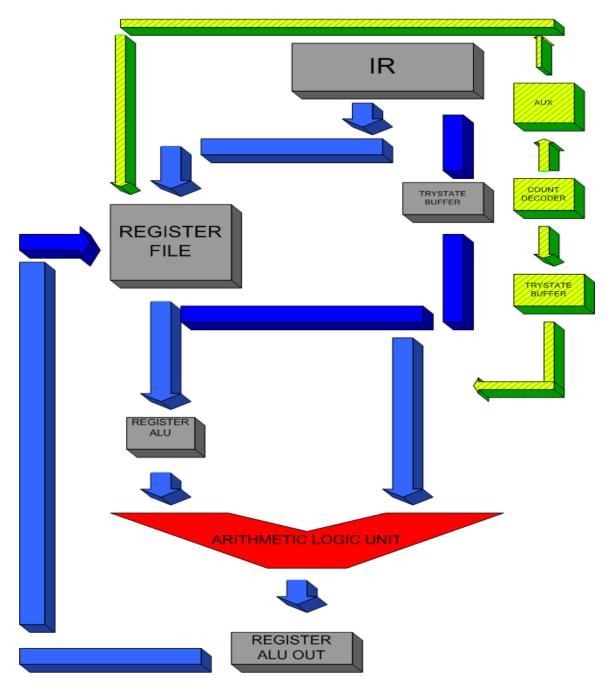

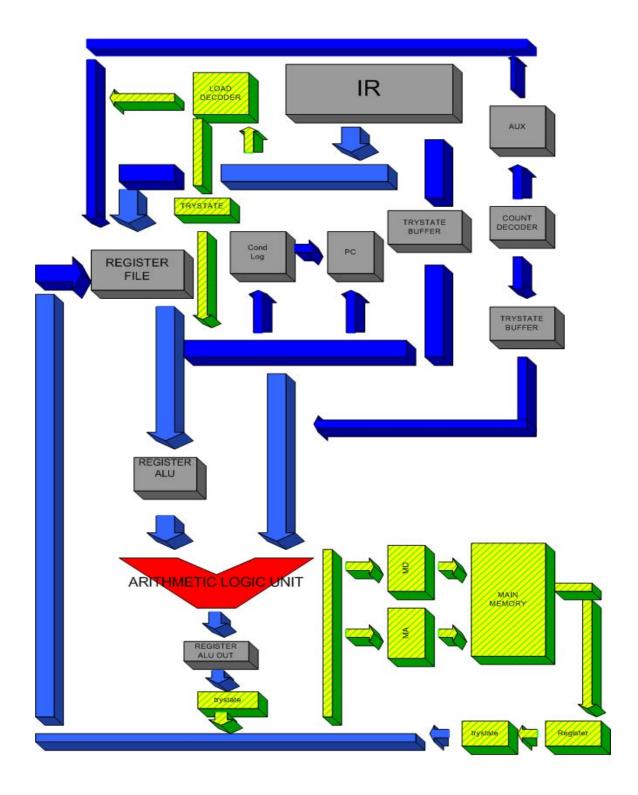

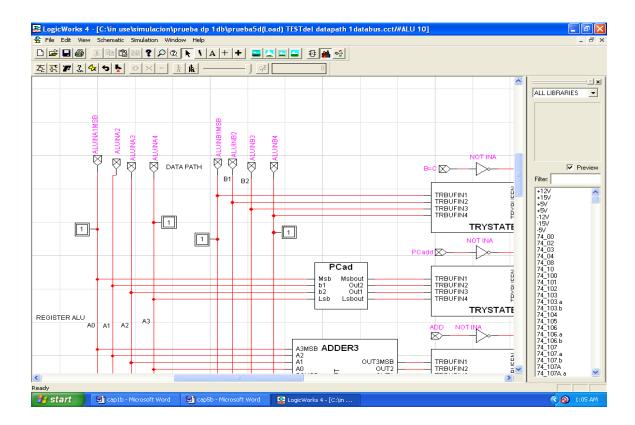

| 5.26 | The Resulting Microcontroller Data Path             | 61 |

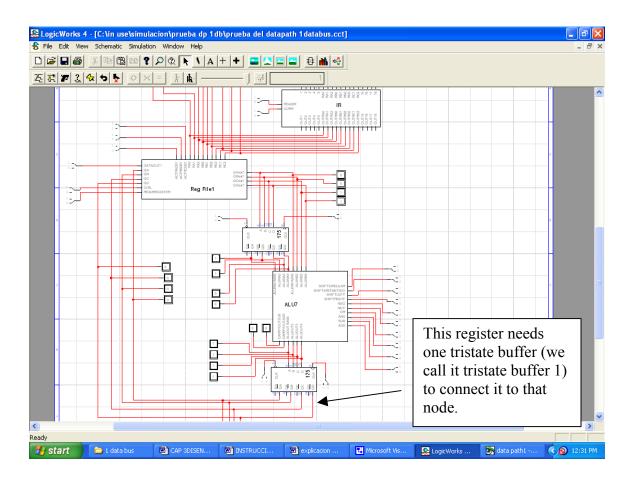

| 5.27 | The Basic Microcontroller Data Path                 | 62 |

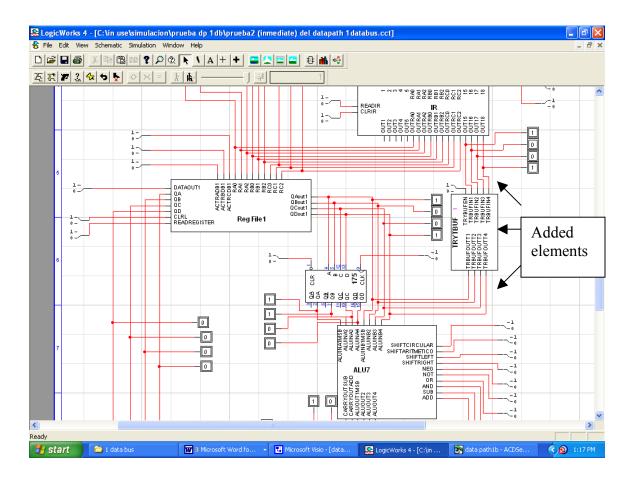

| 5.28 | Added Elements for Immediate Instructions Execution | 64 |

| 5.29 | The Immediate Instructions Circuit Implementation   | 65 |

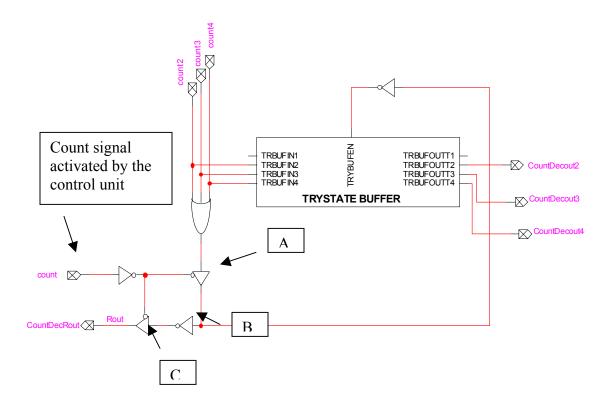

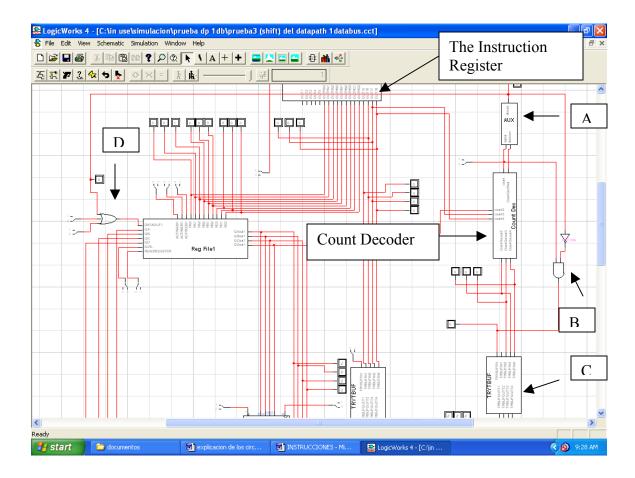

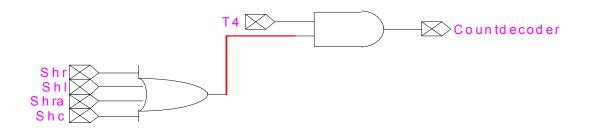

| 5.30 | The Count Decoder                                   | 66 |

| 5.31 | Modified Data Path for Shift Instructions           | 67 |

| 5.32 | The Count Decoder Data Path Implementation          | 68 |

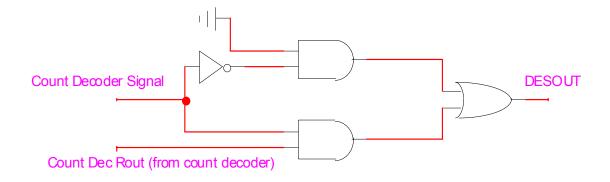

| 5.33 | The Auxiliary Circuit                               | 70 |

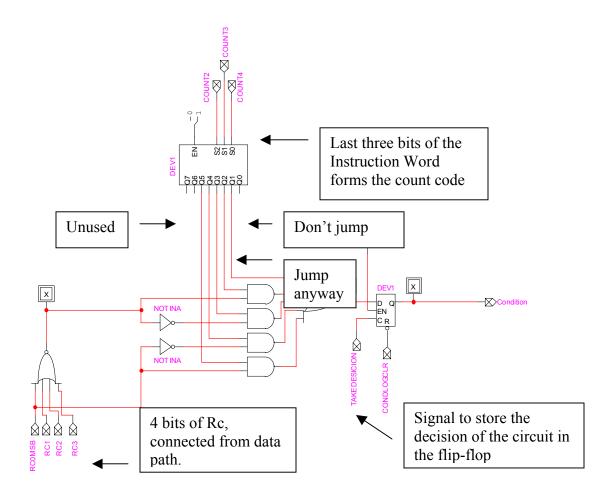

| 5.34 | The Conditional Jump Decoder                       | 71  |

|------|----------------------------------------------------|-----|

| 5.35 | The Program Counter Implementation                 | 73  |

| 5.36 | Memory Rom implementation for Program Storage      | 74  |

| 5.37 | Modified Data Path for Branch instructions         | 75  |

| 5.38 | The Conditional Logic Implementation               | 76  |

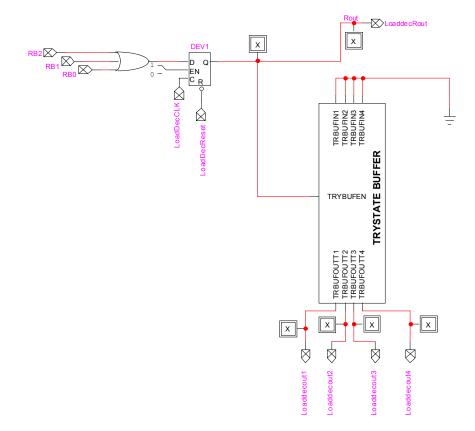

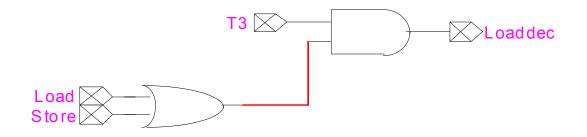

| 5.39 | The Load Decoder Circuit                           | 77  |

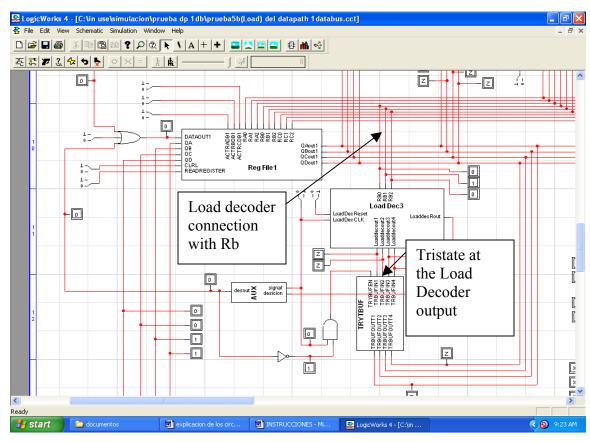

| 5.40 | The Load Decoder Implementation                    | 78  |

| 5.41 | Memory implementation for Load and Store           | 78  |

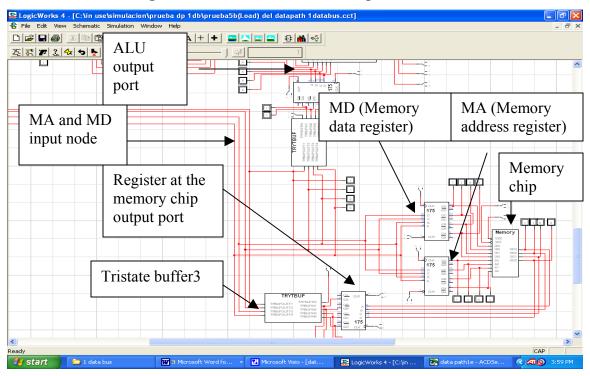

| 5.42 | Added Elements for Load, Store, Read PSW and Fetch | 79  |

| 5.43 | Modified Data Path for Load and Store operations   | 80  |

| 5.44 | In Instruction Hardware Implementation             | 81  |

| 5.45 | Circuit implementation for Out instruction         | 82  |

| 5.46 | Read PSW Instruction Hardware                      | 83  |

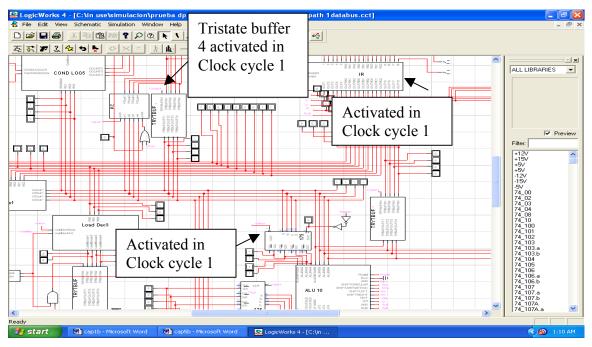

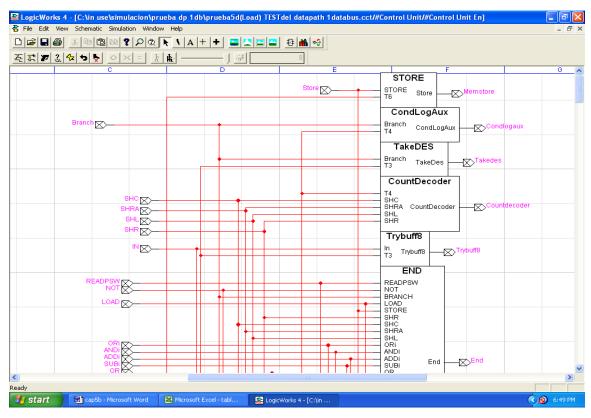

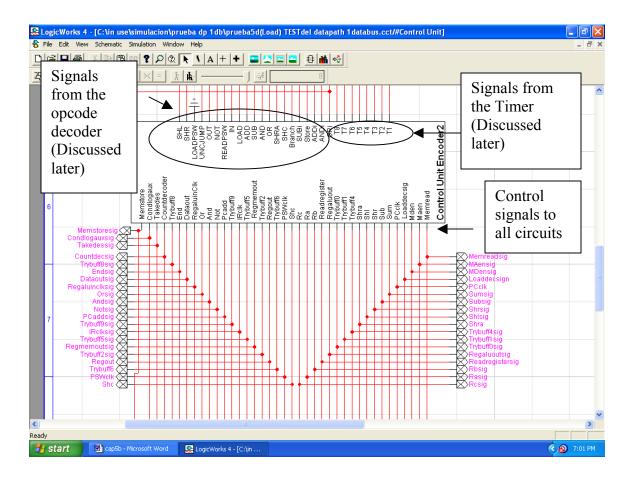

| 6.1  | The Control Unit Implementation                    | 84  |

| 6.2  | Fetch Process First Cycle                          | 86  |

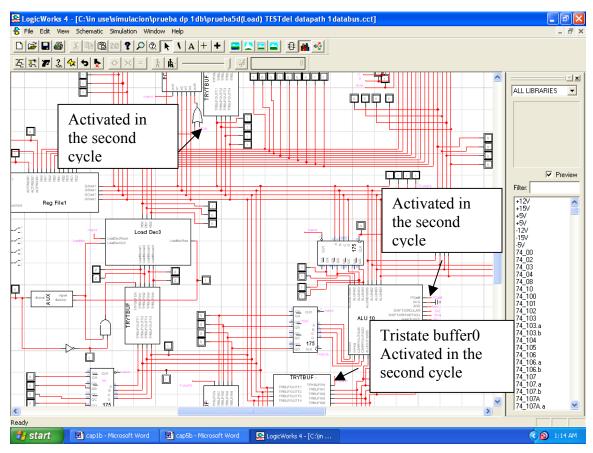

| 6.3  | Fetch Process Second Cycle                         | 87  |

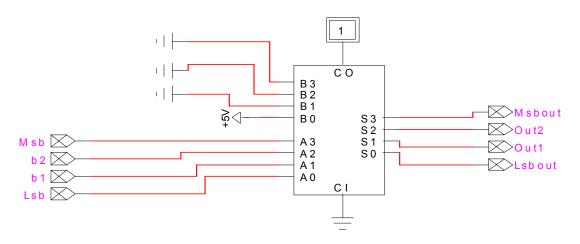

| 6.4  | PC Incrementer Circuit                             | 87  |

| 6.5  | PC Incrementer Implementation                      | 88  |

| 6.6  | Ra signal circuit implementation                   | 100 |

| 6.7  | Regmemout signal circuit implementation            | 101 |

| 6.8  | Reg Alu out signal circuit implementation          | 102 |

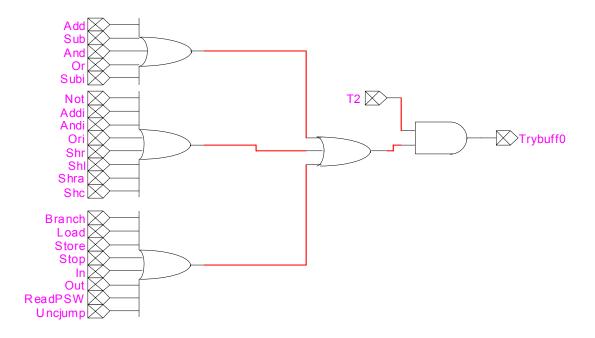

| 6.9  | Trybuff 0 signal circuit implementation            | 104 |

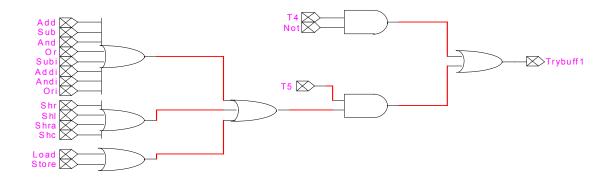

| 6.10 | Trybuff 1 out signal circuit implementation        | 106 |

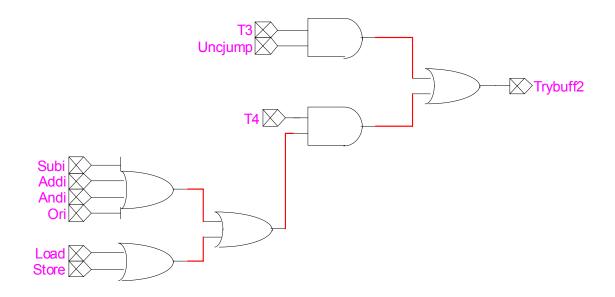

| 6.11 | Trybuf f2 signal circuit implementation            | 107 |

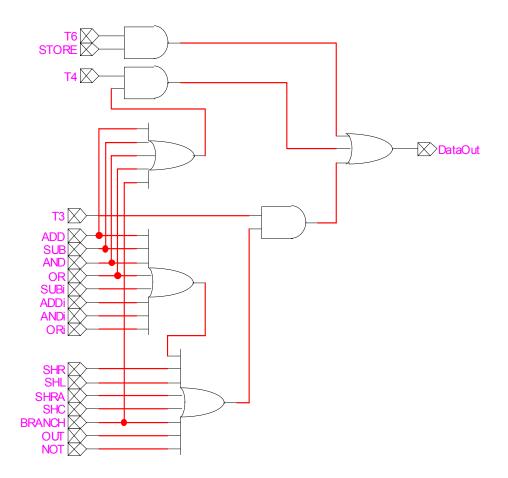

| 6.12 | Data out signal circuit implementation             | 109 |

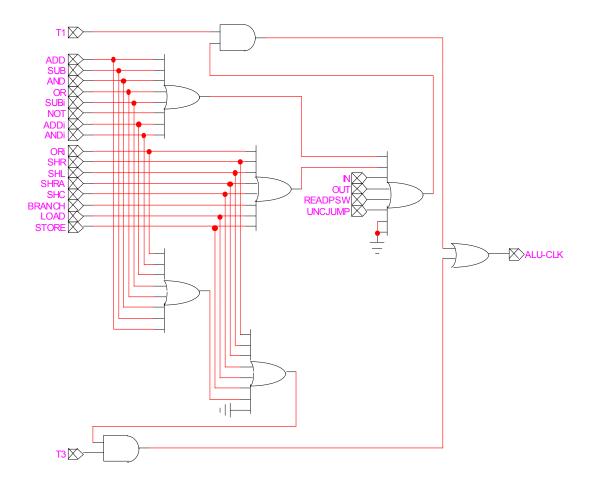

| 6.13 | ALU clock signal circuit implementation            | 111 |

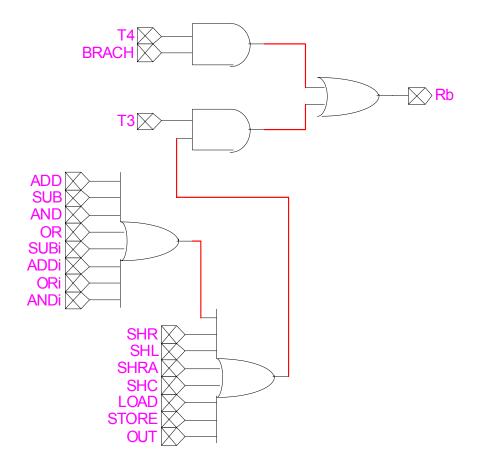

| 6.14 | Rb signal circuit implementation                   | 113 |

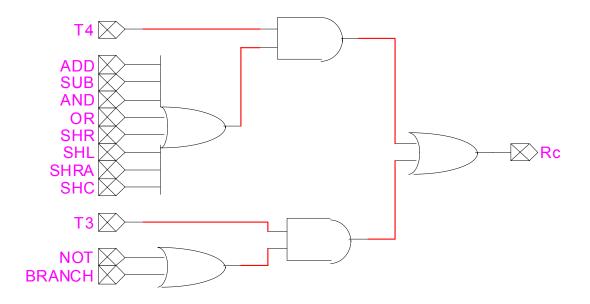

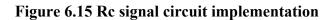

| 6.15 | Rc signal circuit implementation                   | 114 |

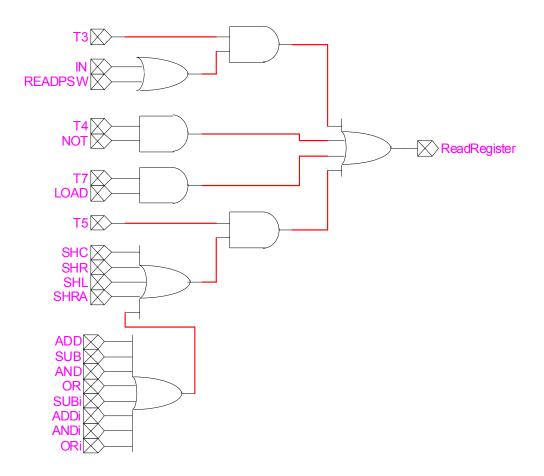

| 6.16 | Read Register signal circuit implementation        | 116 |

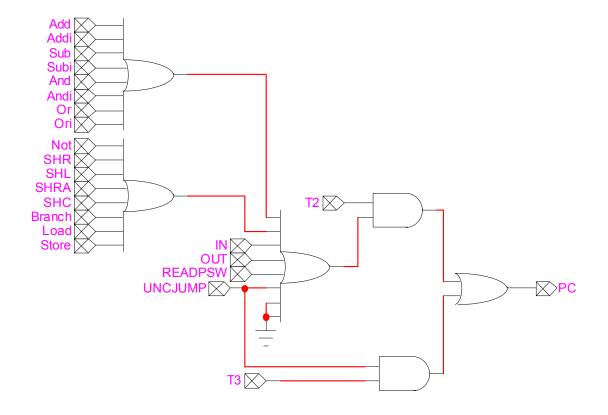

| 6.17 | PC signal circuit implementation                   | 118 |

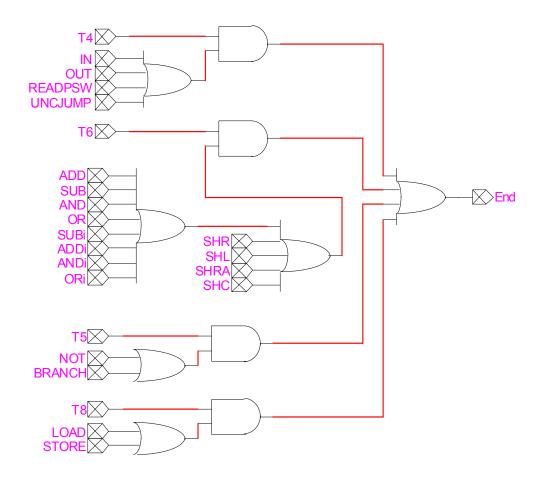

| 6.18 | END signal circuit implementation                  | 120 |

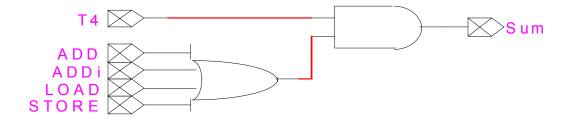

| 6.19 | SUM signal circuit implementation                  | 121 |

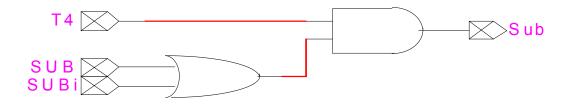

| 6.20 | Sub signal circuit implementation                  | 121 |

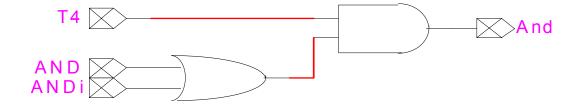

| 6.21 | And signal circuit implementation                  | 122 |

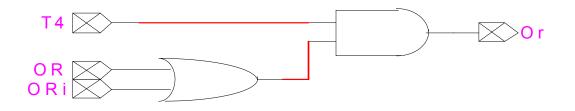

| 6.22 | Or signal circuit implementation                   | 122 |

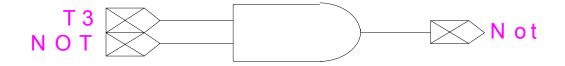

| 6.23 | Not signal circuit implementation                  | 123 |

| 6.24 | Shr signal circuit implementation                  | 123 |

| 6.25 | Shl signal circuit implementation                  | 124 |

| 6.26 | Shra signal circuit implementation                     | 24 |

|------|--------------------------------------------------------|----|

| 6.27 | Count Decoder signal circuit implementation            | 25 |

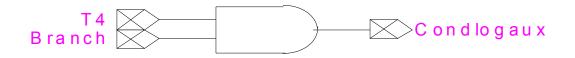

| 6.28 | Conditional Logic signal circuit implementation        | 25 |

| 6.29 | Condlogaux signal circuit implementation               | 26 |

| 6.30 | Load Decoder signal circuit implementation             | 26 |

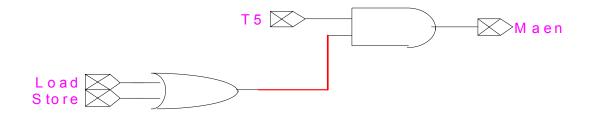

| 6.31 | MDen signal circuit implementation                     | 27 |

| 6.32 | MAen signal circuit implementation                     | 27 |

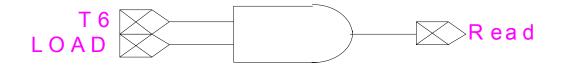

| 6.33 | Read signal circuit implementation                     | 28 |

| 6.34 | Main memory store signal circuit implementation    12  | 28 |

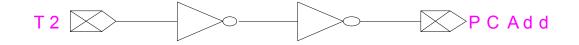

| 6.35 | PC add signal circuit implementation 12                | 29 |

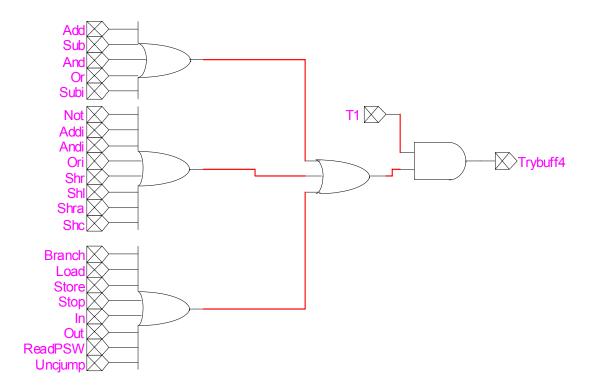

| 6.36 | Try state buffer 4-signal circuit implementation       | 31 |

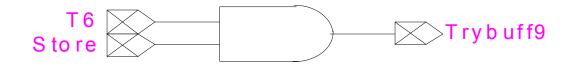

| 6.37 | Try state buffer 9-signal circuit implementation       | 32 |

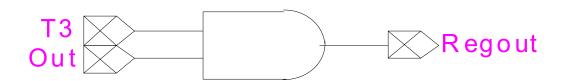

| 6.38 | Regout signal circuit implementation                   | 32 |

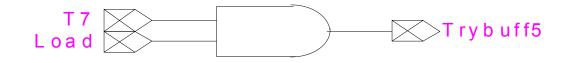

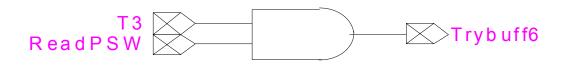

| 6.39 | Try state buffer 5 signal circuit implementation       | 33 |

| 6.40 | Try state buffer 6-signal circuit implementation       | 33 |

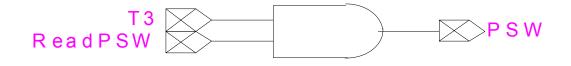

| 6.41 | PSW register signal circuit implementation             | 34 |

| 6.42 | Try state buffer 8-signal circuit implementation    13 | 34 |

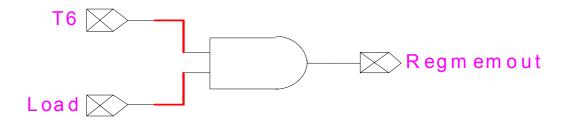

| 6.43 | Regmemout signal circuit implementation   13           | 35 |

| 6.44 | Control Unit Encoder (a)                               | 36 |

| 6.45 | Control Unit Encoder (b)                               | 36 |

| 6.46 | Control Unit Encoder (c)                               | 37 |

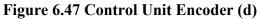

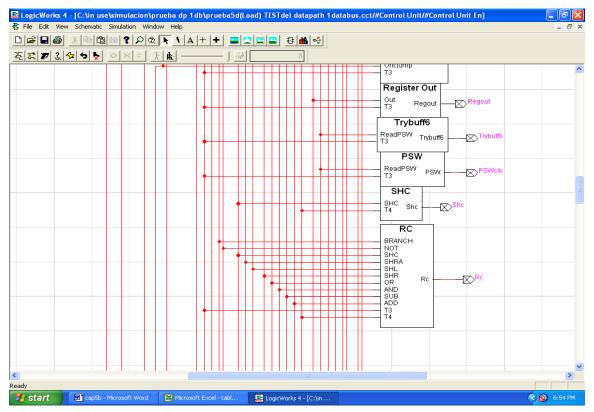

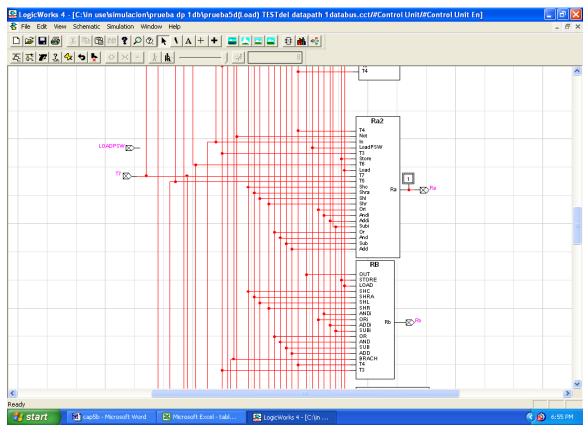

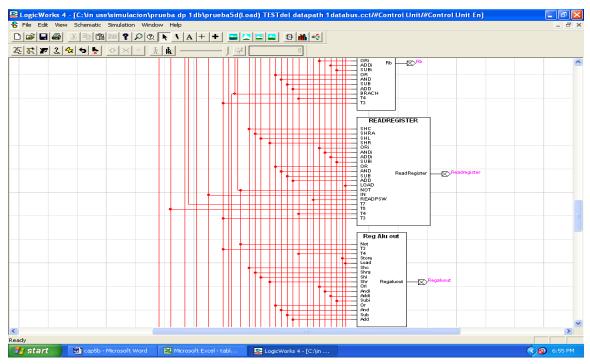

| 6.47 | Control Unit Encoder (d)                               | 38 |

| 6.48 | Control Unit Encoder (e)                               | 38 |

| 6.49 | Control Unit Encoder (f).                              | 39 |

| 6.50 | Control Unit Encoder (g)                               | 39 |

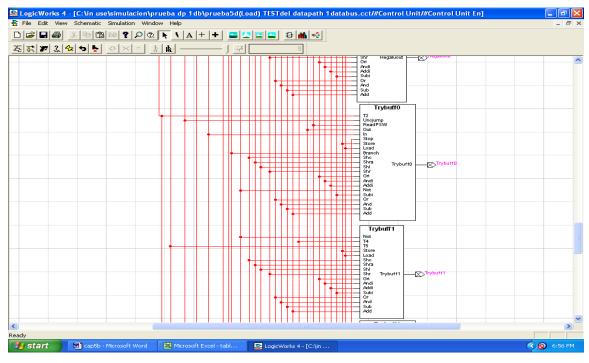

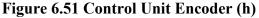

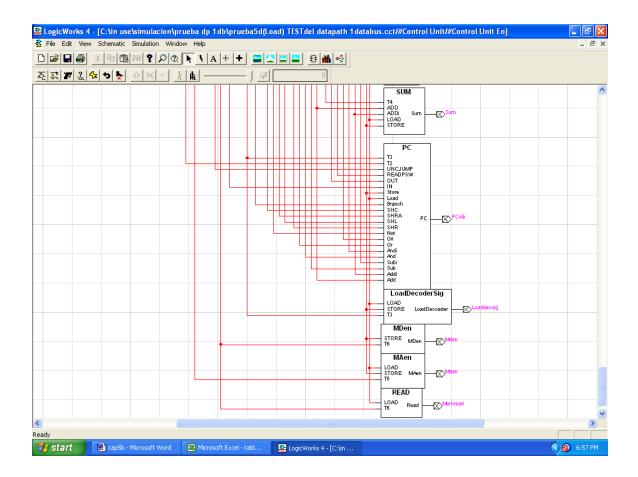

| 6.51 | Control Unit Encoder (h).                              | 40 |

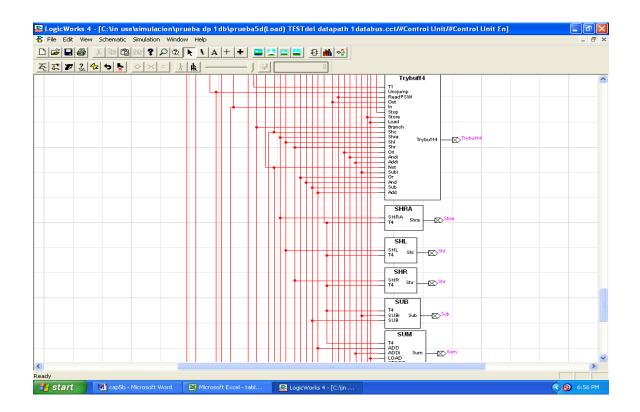

| 6.52 | Control Unit Encoder (i)                               | 40 |

| 6.53 | Control Unit Encoder (j) 14                            | 41 |

| 6.54 | Control Unit Encoder implementation                    | 42 |

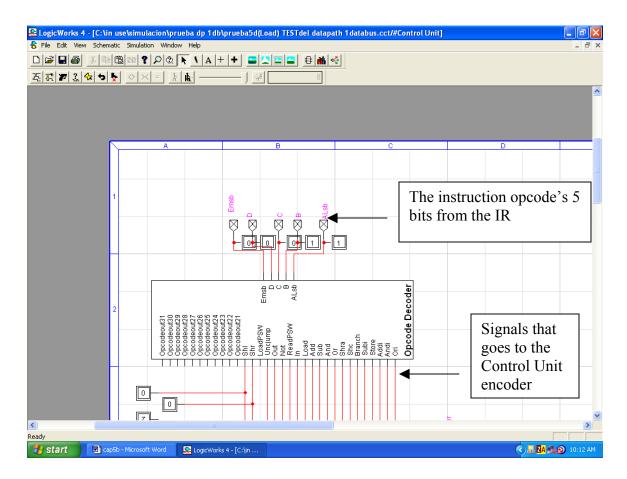

| 6.55 | Operational Code Decoder circuit                       | 44 |

| 6.56 | Operational Code Decoder Implementation                | 45 |

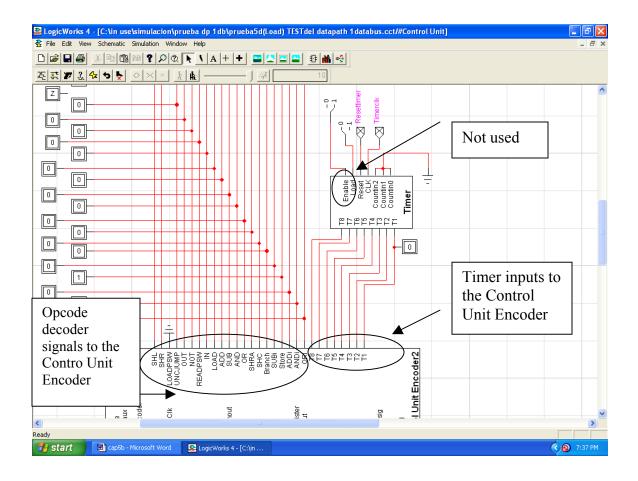

| 6.57 | The Control Unit Timer 14                              | 46 |

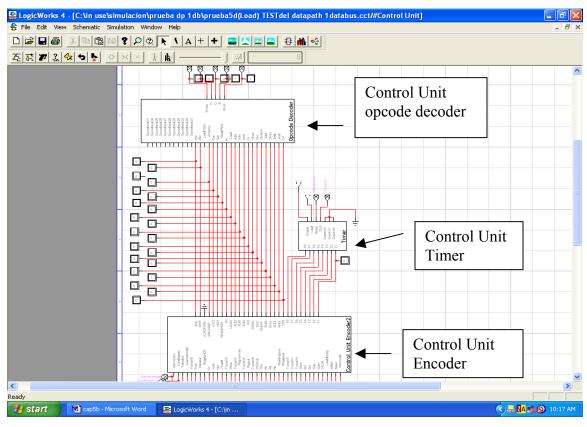

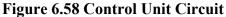

| 6.58 | Control Unit Circuit                                   | 47 |

| 6.59 | Control Unit Implementation                            | 47 |

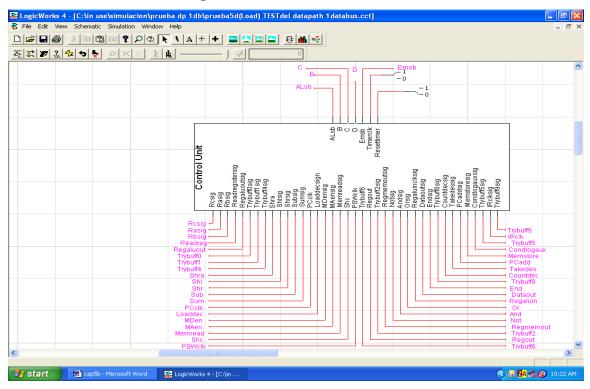

| 6.60 | Delay for signals                                      | 49 |

## **Chapter 1**

## Introduction

Microcontrollers and microprocessors are the most used devices in electronic equipment. Modern technology demands from any engineer, a basic microcontroller or microprocessor knowledge. The basic difference between them is that microprocessors can be configured for the amount of memory and the input / output system used. The microcontroller has all the computing system (I/O system and memory) built in it. Designer's judgment determines which one should be used.

The emphasis of this work will be in the CPU; other important microcontroller parts such as the memory, the I/O system, microcontroller and microprocessor layout, fabrication process and technology are beyond the scope of this work. Design performance parameters like speed, power dissipation, wiring, packing, and transistor sizing are also beyond the scope of this work [8]. Microprocessor Assembly programming is not covered either.

### **1.1 Justification**

The motivation for this work comes after the author took the Computer Architecture undergraduate course. The author realizes that microcontroller design could be an opportunity to summarize and apply most of the electronic engineering basic and advanced courses. Basic circuit analysis, basic electronic course, digital logic circuits and advanced digital design are some of the electrical engineering courses used in this work. Another motivation for this work lies in the author's desire to present the student the microcontroller concepts, design and operation, as quick and clear as possible. For many years literature has been published regarding microcontroller and digital design. Techniques, methods, and procedures have been published, but most of them are usually explained using a symbolic or algorithmic approach. Some examples of this kind of approach can be found on "The Intel Microprocessors 808X,Pentium and Pentium Pro"[22], "Computer Organization and Design The Hardware / Software Interface"[21], Embedded Systems and Computer Architecture"[19],Computer Organization and Architecture Principles of Structure and Function [20].

Although this work can serve as a quick reference for people with some microcontroller basic knowledge, it was developed specially for people that have not been exposed to microcontrollers or are exploring the field for the first time. After students understand the basic microcontroller concepts, they can go by their own in the field exploring other design concepts and alternatives.

To grasp the basic concepts at the starting stage, students feel more comfortable when they see the theoretical materialization, simulation and execution of hardware circuits, instead of large equations, diagrams, algorithms and symbols that most of the microcontroller information sources offer. The hardware implementation of every concept is what makes this work useful for beginners to learn and understand microcontroller concepts.

One of the main features of this work lies in the fact that it follows a series of steps and makes emphasis on the most important points in each and everyone of those steps. Beginners just have to follow those steps in order to design and simulate their own microcontroller. This work illustrates the design, simulation, testing, and implementation of all microcontroller circuits in each step. Through the whole process the student will appreciate the complete microcontroller evolution and transformation from zero to a functional unit.

Practice is the key for success in any career. This method provides mechanisms to change some of the microcontroller parts without affecting others. It makes emphasis on modularization. Through the whole process, modules of each part are designed and can be changed individually without affecting the entire system. This allows experimentation and circuit changes to examine what happens.

One possible application of this work is that students can transform the microcontroller schematic into HDL code and download it to an FPGA for prototype simulation. This way, the students increase their understanding of microcontroller concepts and operation, with hands-on experience; they can examine how the instruction execution is and how the microcontroller circuits work in every instruction. Also multiple versions of one microcontroller can be developed with slight changes, allowing students to observe the effect of those changes in each design and simulate each prototype on FPGA. This work provides a mechanism for students to train easier, faster and get more practice in microcontroller design.

A weak point of this method is that it does not achieve an efficient implementation. Performance is not the main point of this work; just delivering to the student the most important microcontroller concepts. In chapter two we find information regarding to microcontroller performance. The focus of this work is in the methodology, not in the computational capabilities and features of the microcontroller.

Besides its educational approach, another important point is that this method provides a mechanism to design a microcontroller that can be simulated, as said before, on FPGA, but also can be used on real applications. In other words, users making slight changes can produce a different microcontroller for new applications as needed. Users do not have to buy a new microcontroller but try a different one using this method. Of course this is convenient for experimentation or academic purposes only, not for applications where performance is the critical point. Modern microcontroller costs are relatively low, and are very useful for many applications but sometimes there are situations that are better handled with specially designed microcontrollers for specific applications. For example, a designer may want to build and control his/her own personal robot, with a specific instruction set. Designers can find in the market some inexpensive microcontrollers that suit design requirements. But those popular microcontrollers perhaps are for general use, but probably lacking features that designers would be looking for.

It is important to remember that those popular microcontrollers in the market today are not designed for specific needs; some are for general purpose and others are for specific applications. Then, sometimes designers invest huge amounts of time and effort designing and programming assembly routine codes in order to achieve the required microcontroller performance, as to take full control of their robot. Designing a microcontroller for specific needs allows designers to minimize the programming complexity and enhance designers system's performance.

Designers also should keep in mind that microcontroller programming is as important as the microcontroller hardware design. Although it is not the intention of this work to discuss the microcontroller programming, this work illustrates the instruction execution of the microcontroller. This helps a lot when we are trying to understand the basic concepts of assembly programming like the addressing modes, clock cycles, and operands.

The quality of the microprogramming is what makes it possible to transform the complex circuits of the microcontroller into something useful. One of the main motivations for this work will be that inexperienced designers will not only gain an insight of microcontroller design and operation, but also, designers will get a better understanding of the microcontroller assembly programming.

#### **1.2 Research Objective**

The main idea of this work is to develop a systematic and straightforward procedure that allows students to understand microcontrollers design and operation. Inexperienced designers should be able to design their own microcontrollers from scratch using this procedure. This work assumes that the student has a basic knowledge of circuit analysis and digital logic circuits.

#### **1.3 Simulations**

There are many simulation tools that can be used for microcontroller design. Hardware Description Language (HDL) programming and graphic simulators are the main development tools used in the microcontroller design market. The computer tool used in this work is the graphical simulator Logic Works. Logic Works was chosen because the focus of this work is for beginners in the microcontroller field. Logic Works brings to the student an easy and complete visualization of the circuits and their operation. One of the main features of this work consists in its illustrative techniques and Logic Works results useful for these purposes.

HDL is convenient for large size circuits and then its code can be downloaded into an FPGA for device prototype testing. But its programming nature does not result useful for people trying for the first time to grasp the microcontroller concepts. Users face a double challenge because they are trying to understand the basic principles of the microcontroller operation and at the same time they are trying to learn the programming rules and techniques of HDL code in order to execute the circuit simulation. Logic Works allows users to graphically understand what happens inside the microcontroller during its execution and then, schematics can be transformed into an HDL code and downloaded into an FPGA for further prototype simulation.

#### 1.4 Work Organization

Basic theory about microprocessors, its basic concepts and applications, performance factors and a comparison between microcontrollers and microprocessors are discussed in Chapter 2. The third chapter discusses the digital circuits available for the microcontroller HDL code prototype, the microcontroller implementation alternatives and programming. The fourth chapter describes in detail each of the microcontroller design steps used in this work and the most important points to keep in mind. Chapter 5 has an example of the microcontroller design process described in chapter four. In this chapter the microcontroller instruction set, architecture, basic circuits and the evolution of the data path as new instructions are developed are described in detail. Chapter 6 presents the control unit design. A detailed description of each instruction is given in chapter 7. Chapter 8 presents the conclusions of this work.

## **Chapter 2. Theory and Applications**

### 2.1 Microcontroller Applications

The microcontroller is one of the most important electronic devices on which modern technology is based on. Microcontroller uses are endless; from toys to microwaves, ovens, TV sets, computers, printers, cars and so on.

Digital circuits become larger and larger as more functions need to be executed. In modern digital world, most individual digital circuit components are sold in a single chip. Those individual chips need power and space to operate. When the circuit becomes huge, the traditional logic design approach is not the best option and microcontrollers become convenient. Microcontrollers are basically sequential machines because their operation depends on their current status and its inputs. Their power lies in the fact that the hardwire configuration allows its operation to be changed depending on programming. It is not required to use additional logic circuits if the operation is changed.

#### 2.2 The Processor and the Microntroller Concepts

Data are words, numbers and graphics that describe people, events, things and ideas. It becomes information when used as the basis for initiating some actions or to take decisions. Data is represented by binary expressions when used in the digital world.

A binary number system is a numeric system that has only two different digits: 1 and 0 (binary); and any of these is called a bit. Data are represented by finite permutation of bits. These combinations are called words. A collection of hardware devices that manipulate binary expressions to process information is called a processor [1].

The processor manipulates binary numbers following an algorithm, which determines the way in which the instructions are processed by the hardware inside the processor, how data begins to be processed and where it is finished. An instruction code in the instruction format indicates to the system which algorithm to perform. This specific algorithm represents the specific instruction to be executed. The following are the principal processor components [1].

- 1) Arithmetic Logic Unit (ALU): is a combinational logic network that performs the mathematical and logical operations of the processor.

- 2) Registers: hold the data operated on, between clock cycles for processing.

- 3) Control Unit: a synchronous sequential logic network that controls all the hardware in the digital system. This unit decodes the instruction,generates the proper sequence of control signals, and activate and deactivates the corresponding hardware units in the system to achieve the right processing according to the instruction.

- 4) The clock: a periodic pulse waveform that synchronizes all the elements in the system. Every clock cycle represents a state of the system. This means that in every clock cycle the system will have specific hardware control lines that are going to be on or off. The system clock speed depends on the response speed of the circuit elements when data passes through them.

Although these components are the most important ones, they are not alone. A big difference exists between identifying all those main elements and putting them together to work. Digital Logic, gates, multiplexers and other important circuits are necessary for processing support or to solve implementation problems, avoid signal conflicts and so on. Memory (circuit where data and instructions are stored) and input / output circuit interface (computer system used to pass data to and from the central processing unit) are necessary circuits for the microprocessor implementation.

Any hardware involved in data transfer into or out of the processor is considered separate from the processor. Processor only refers to the hardware that manipulates data. When a processor is capable of performing arithmetic operations, logical operations, load and store operations, branching operation and input-output operations, it is called a "general purpose processor". When it is integrated in a single IC it is called a microprocessor.

A personal computer is usually a connection of components that contain many microprocessors. The motherboard contains the main microcoprocessor, but other microcoprocessors or microcontrollers are also involved. The keyboard, the disk drive interface, the display monitor interface, and the printer are some of the components that may contain their own microcontrollers. Therefore, a personal computer system is a collection of many microcontrollers controlled by a main microprocessor.

#### 2.3 Microcontroller Performance Factors

Microcontroller performance can be defined in terms of speed, size, power, cost, design time and manufacture cost. Each depends on concepts beyond the scope of this work. The main factor determines the microcontroller performance [9] are its architecture, design features and manufacture process. Thus the microcontroller performance depends on designers' judgment at the design stage.

The architecture features determine the remaining microcontroller characteristics. The architecture depends on the microcontroller application. Different applications differ in features and data processing requirements. The Von Neumann architecture and the Harvard architecture [3] are the two main architectures used in microcontroller design. The Harvard architecture is the most popular nowadays. Von Neumann architecture main characteristic is that it uses one main memory where data and instructions are stored. Only one system bus is used for control, data transfer, processing and addressing. Harvard architecture consists of two different and independent memories in which one contains instructions and the other one contains data. Both have their own data bus systems for control, data transfer, processing and addressing. Both memories can be accessed simultaneously.

After the architecture has been defined the design process will be ruled by it. The hardware implementation will process the data by the architecture definition. Every part of the microcontroller hardware has many variables that can be configured to set its operation. Examples of these variables are the chip area and the distance between its components, the chip power dissipation, wiring effects, chip speed, manufacture materials, and packing. Each and every one of those variables is a field of study by itself, but they are beyond the scope of this work [8].

The Architecture and the hardware implementation features transform an idea into a circuit with specific characteristics. Computer simulation allows designers to verify that circuits work as required. When specification constrains and performance requirements are met, it is time for testing and manufacture. Design aspects defined by the architecture determines which manufacture process will be used. Manufacture processes have advantages and disadvantages and they can differ in equipment cost and technology.

#### 2.4 The General Purpose Microcontroller

Microcontrollers execute different kind of instructions. The instructions for a general-purpose microcontroller can be:

- 1) Arithmetic Instructions.

- 2) Logic Instructions.

- 3) Data transfer Instructions.

- 4) Jump Instructions.

- 5) Miscellaneous Instructions.

Some microcontrollers are designed to specialize their execution in one or more of those classifications. Those are special purpose microcontrollers. Those basic instructions are combined to perform more complex instructions and the power and speed of execution of the microcontroller allows those instructions to execute complex tasks. Instructions are executed in such a way that an operation is achieved and different operations are used for different applications.

Special purpose microcontrollers are designed for an application where using a general-purpose microcontroller is not the best option. Usually those applications require repetitive execution of one or more instructions, which can be implemented in software or hardware. Hardware instruction implementation allows faster execution and reduces program size. Examples of special microcontrollers can be found on camcorders, digital cameras, automobiles and so on.

#### 2.5 Comparing Microcontrollers and Microprocessors

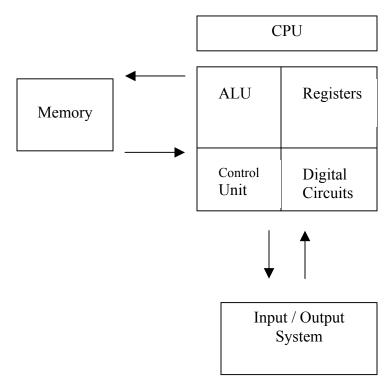

The microprocessor is an integrated circuit composed by the Control Unit, Arithmetic Logic Unit, Registers and Digital circuit support. The microprocessor uses its data bus pins, address bus pins, and control lines pins to allow connection to other circuits to configure the entire system. The main characteristic of the microprocessor is that it is an open system, which means that its configuration is variable, and can be adapted to many different applications. A block diagram of a microprocessor is shown in figure 2.1.

**Figure 2.1 The Microprocessor Configuration**

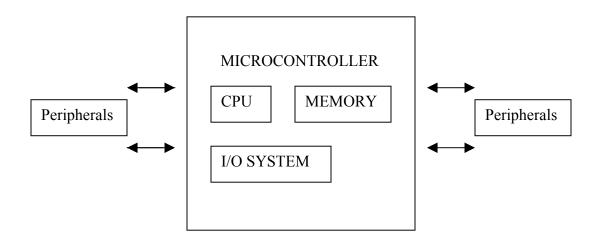

The microcontroller is a closed system. In the microcontroller all parts that can be configured in the microprocessor are fixed in the same chip. A block diagram of a microcontroller is shown in figure 2.2. Just the lines that control the peripherals are the ones that go outside the chip. This characteristic makes microcontrollers suitable for specific applications or for general use.

The microcontroller applications range is narrower than the microprocessor's range. The reason is that microcontrollers have all their computing system integrated on the same chip. This reduces the available space inside the microcontroller to include components that the microprocessor have externally like memory and I/O system.

This means that a microprocessor can be used for microcontroller applications but microcontrollers cannot always be used for most microprocessor applications. Microcontrollers are preferred when the application is defined and specific. In those situations where important system modifications are needed or applications are not specialized a microprocessor is more convenient.

**Figure 2.2 The Microcontroller Configuration**

## **Chapter 3 Microcontroller Implementation and Operation**

## **3.1 Implementation Alternatives**

Traditionally, digital design was a manual process of designing and capturing circuits using schematic entry tools [2]. The increase in size and complexity of hardware has forced designers to discus new methods and tools for digital design.

Hardware description languages (HDL) and synthesis, have substituted the more traditional schematic process of simulation. This is because HDL allows simulating circuits with hundreds of elements in a relative short period of time. Some of the new tools for HDL simulation are electronic equipment containing Application-Specific Integrated Circuits (ASICs), or Field-Programmable Gate-Arrays (FPGAs).

The introduction of industry standards for hardware description languages and commercially available synthesis tools has helped establish this revolutionary design methodology. Some advantages are:

- Increased productivity yields shorter development cycles with more product features and reduced time to market,

- Reduced Non-Recurring Engineering (NRE) costs,

- Design reuse is enabled,

- Increased flexibility to design changes,

- Faster exploration of alternative architectures

- Faster exploration of alternative technology libraries,

- Enables use of synthesis to rapidly sweep the design space of area and timing, and to automatically generate testable circuits,

- Better and easier design auditing and verification.

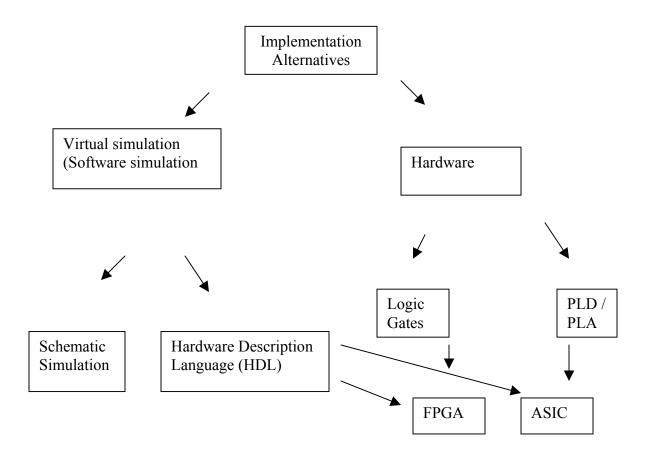

**Figure 3.1 Microcontroller Implementation Alternatives**

Figure 3.1 illustrates the alternatives of hardware implementation available. Modern designs are characterized by their increase in size and complexity, circuit simulation is one of the most important steps in circuit design. Circuit simulation and hardware prototype implementation saves time and money because they allow designers to verify that the implemented digital design works as required. Software simulation previews the circuit behavior. It serves as a mechanism to verify accurately the principal circuit characteristics and to ensure its design requirements. Hardware implementation, in contrast with software simulation, is a physical prototype configuration that serves to physically simulate the circuit behavior. Note that hardware implementation requires software simulation through HDL. Its advantage lies in the fact that circuits can be tested interacting with other real physical circuits before they are fabricated.

Standard "off-the-shelf" integrated circuits have a fixed functional operation defined by the chip manufacturer. Contrary to this, both ASIC and FPGAs are types of integrated circuit whose function is not fixed by the manufacturer. The designer for a particular application defines the function. An ASIC requires a final manufacturing process to customize its operation while an FPGA does not.

#### ASICs

An Application-Specific Integrated Circuit is a device that is partially manufactured by an ASIC vendor in generic form. This initial manufacturing process is the most complex, time consuming, and expensive stage of the total manufacturing process. The result is silicon chips with an array of unconnected transistors. The final manufacturing process of connecting the transistors together is then completed when a chip designer has a specific design to implement using ASIC. An ASIC vendor can usually do this in a couple of weeks and is known as the turn around time. One problem is that it is a physical realization, which means that if there are mistakes during the HDL simulation and are not corrected, its physical implementation will have the errors also and there are no mechanism to correct it once it is fabricated. There are two categories of ASIC devices: Gate Arrays and Standard Cells.

#### Gate Arrays

There are two types of gate array; a channeled gate array and a channel-less gate array. A channeled gate array is manufactured with single or double rows of basic cells across the silicon. A basic cell consists of a number of transistors. The channels between the rows of cells are used for interconnecting the basic cells during the final customization process. A channel-less gate array is manufactured with a "sea" of basic cells across the silicon and there are no dedicated channels for interconnections. Gate arrays contain from a few thousand equivalent gates to hundreds of thousands of equivalent gates. Due to the limited routing space on channeled gate arrays, typically only 70% to 90% of the total number of available gates can be used.

The library of cells provided by a gate array vendor will contain: primitive logic gates, registers, hard-macros and soft-macros. Hard-macros and soft-macros are usually of MSI and LSI complexity, such as multiplexers, comparators and counters. The manufacturer in terms of cell primitives defines hard macros. By comparison, the designer, for example, characterizes soft-macros by specifying the width of a particular counter.

#### Standard Cell

Standard cell devices do not have the concept of a basic cell and no components are prefabricated on the silicon chip. The manufacturer creates custom masks for every stage of the device's process and silicon is utilized much more efficiently than for gate arrays.

#### FPGAs

The Field-Programmable Gate Array is a completely manufactured device, but remains design independent. Each FPGA vendor manufactures devices to a proprietary architecture. However, the architecture will include a number of programmable logic blocks that are connected to programmable switching matrices. To configure a device for a particular functional operation these switching matrices are programmed to route signals between the individual logic blocks.

#### PLD and PLA

The Programmable Logic Device (PLD) is essentially a grid of programmable conductors that form rows and columns with fusible link at each cross point. PLD are classified according to their architecture, which is basically the functional arrangement of internal elements that give a device its unique characteristic. The Programmable Logic Array (PLA) is a device with programmable AND and OR arrays.

## **3.2 Hardware Description Languages (HDLs)**

A Hardware Description Language (HDL) is a software programming language used to model the intended operation of a piece of hardware. There are two aspects of hardware description that HDL facilitates: true Abstract Behavior Modeling and Hardware Structure Modeling.

The Abstract Behavior Modeling is a declarative hardware description language in order to facilitate the abstract description of hardware behavior for specification purposes. The Hardware Structure Modeling is a hardware structure that can be modeled in a hardware description language irrespective of the design behavior. The hardware behavior may be modeled and represented at various levels of abstraction during the design process. Higher-level models describe the operation of hardware abstractly, while lower level models include more detail, such as inferred hardware structure [23].

## **3.3 Tradeoffs in Microcontroller Design**

Is it necessary to use a special purpose microcontroller or a general purpose one can be used? That is an important question that must be answered before attempting to implement a microcontroller. In addition to having the basic instruction set, special purpose microcontrollers usually have instructions specialized to perform specific tasks. Those microcontrollers include in their design, special hardware that is used for execution and calculation support to execute instructions in their specific applications.

The application determines the microcontroller operation, and the operation is executed with specific instructions. Then, the real deal in the design process consists in making tradeoffs between designing more powerful and complex instructions that reduce the programming code, or as another alternative, the operation can be implemented in hardware to save the time-consuming programming of certain tasks and achieve faster execution.

Should an operation be implemented in hardware or software? Is it worth? The answers to those questions depend on many factors like design requirements, available budget, technology used and so on. Hardware instructions implementation result in faster executions but increase design cost. Software implemented operations save hardware and costs but increase the instruction execution time and the programming complexity. There are not defined rules. Designers have to make their choices based on design constrains and available resources to produce the best system performance at the lower cost.

## 3.4 The Microcontroller Programming

Commonly, every processor is designed with one purpose and has its own instruction set. The microcontroller architecture determine how powerful the instruction set is and how many clock cycles it takes to execute its instructions. As the instructions are more powerful, the microcontroller programming usually becomes more complex but shorter and more tasks are done per clock cycle.

Microcontroller programming is usually done in assembly language. This is because this is a low level programming language. Instruction in this low level programming language are directly related to the machine code, the ones and zeroes or high and low voltage combinations necessary to control all the hardware inside the microcontroller to process data. One advantage of assembly language is that allows the programmer to control some internal process like selecting specific registers that normally cannot be done using a high level programming language.

Each microcontroller has its own assembly language code, so the assembler is specific to the microcontroller. High level programming languages, on the contrary, are independent of the processor. The compiler and other tools are transparent to the programmer, do the translation to the respective processor used by the computing system.

Commercial microcontrollers are very often sold embedded in the so-called evaluation cards. These system boards contain additional hardware and connectors to facilitate applications and programming. The programmer can design the assembly program and download it to the microcontroller easily.

## **3.5 The Microcontroller Operation**

Summarizing, the microcontroller operation consists in three steps:

- Fetch process; the fetch process consists in retrieving one instruction from memory and load it in the Instruction Register.

- Decoding; once the instruction is in the Instruction Register, the control unit receives the operational code from it. The control unit decodes the operational code to identify the instruction to be executed.

- Executing; after the control unit identify the instruction, it start a series of microcontroller hardware signal activations. To carryout the execution process some of the circuit elements must be on and off in each clock cycle. The control unit ensures that the necessary elements are on and off in each clock cycle to accomplish the instruction execution.

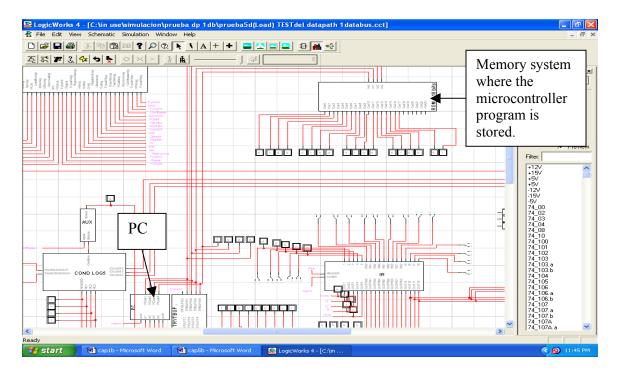

Basically the CPU addresses a memory location, obtains (fetches) a program instruction that is stored there, and carries out (executes) the instruction. After completing one instruction, the CPU moves on to the next one. This fetch and execute process is repeated until all of the instructions in a specific program are done. The fetch process clock cycle depend on the Instruction Register size (and i.e. the instruction word) and the number of bits of the data bus. For example if the IR size is eighteen bits and the data path is four bits, then five clock cycles will be needed for the fetch process. The memory size will determine how many instructions can be stored in it and indeed the program size that can be stored.

## 3.5.1 The Program Counter

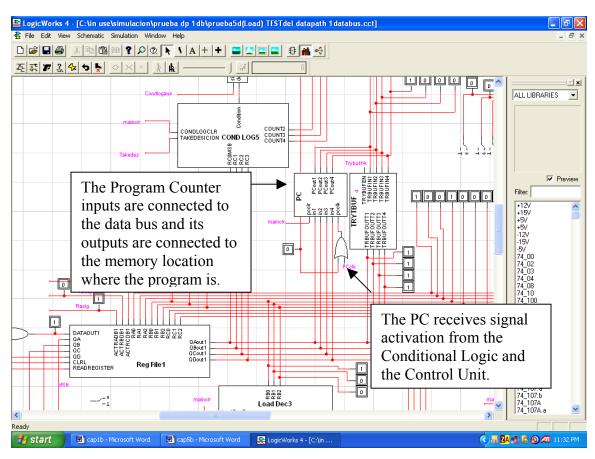

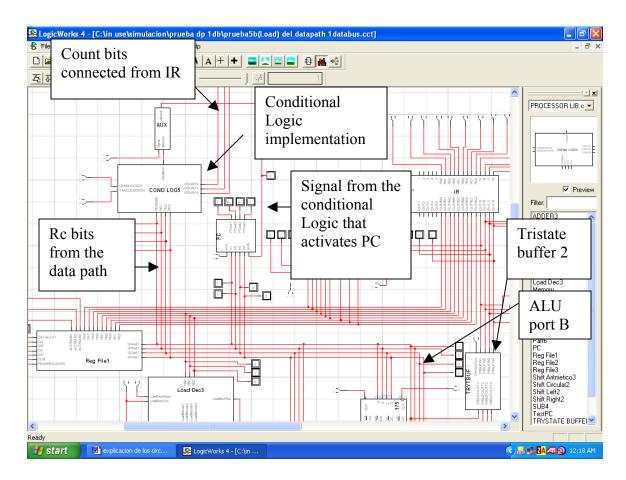

To indicate the memory address to retrieve the instruction a special register is used. This register is the Program Counter. The PC holds the address of the memory location where the next instruction is located. The PC input ports are connected to the data bus; in this way the ALU connected also to the data bus increment the PC to the next memory location. The PC output port is connected to the memory address port to identify the required memory location where the instruction is.

## **3.6 FLAGS**

Flags are also called conditional codes. Condition codes are bits set by the CPU hardware as the result of operations. Usually condition codes are collected into one or more registers called flag register. Flags are very useful because they can be used as parameters to make decisions. For example, a microcontroller application can check the flag register to see if the result of one subtraction operation is zero, then, using this information the microcontroller can take decisions to execute other instructions.

## **Chapter 4 The Microcontroller Design Steps**

This chapter describes the steps used in the microcontroller design example of this work. Each step has important points that designers should keep in mind in them. Those points guide the user through the whole design process.

## 4.1 Methodology Steps

The steps are enumerated in table 4.1

| STEP      | DESCRIPTION                                            |

|-----------|--------------------------------------------------------|

|           |                                                        |

| STEP I    | Justification                                          |

| STEP II   | Operations Definition                                  |

| STEP III  | Instruction Set Definition                             |

| STEP IV   | Architecture Definition                                |

| STEP V    | Arithmetic Logic Unit (design and implementation)      |

| STEP VI   | The Register File                                      |

| STEP VII  | The Instruction Register                               |

| STEP VIII | Data Path for data processing and Control Signal Table |

| STEP IX   | The PC, Jump and data transfer instructions            |

| STEP X    | The Control Unit                                       |

#### **Table 4.1 Methodology Steps**

The description of each one is given next.

## 4.2 Steps Description

#### **STEP I: Justification**

Designers should first analyze the situation and decide if a microcontroller is needed for the application. The following are some questions that could guide designers at the implementation decision stage.

- What is the application? Application is a computer program or set of programs designed for a particular type of real world job.

- Can the application be implemented with logic circuits? The answer to this question is obviously yes. But, what will be the resulting circuit size? Is it affordable?

- What could be the microcontroller implementation advantage? The importance of microcontroller lies on the fact that it has hardwired circuits that change their operation using programming. Designers should analyze if the amount of different applications justify the use of a microcontroller or if the use of individual operational circuits is more convenient.

- What are the advantages or disadvantages of using a microcontroller in terms of efficiency, time, design complexity and cost? Analyses of tradeoffs are necessary to answer those questions. Budget and design requirements analyses are necessary to decide if a microcontroller use is convenient or not. Sometimes the use of a microcontroller results in a waste of hardware resources. In other situations the microcontroller use results in the less expensive option. There are situations in which programming is avoided using logic circuit, but this choice could result in larger, expensive and more complex circuits.

- Is a microcontroller result in the best option? How many different operations will be used? How many times one operation is executed? Is it better to use individual circuits for every operation or using a microcontroller is more efficient? Do Individual circuits have faster response than the microcontroller? Is this difference in time response needed for the application? Is the microcontroller programming complexity worth instead of using individual circuits? What tasks are done routinely?

# **STEP II: The Operation Definition**

After a careful study of the application, the next step consists in defining the amount of different operations required for the application.

One computer operation is defined as the calculation executed by a single machine code instruction [8]. It is also the mathematical or logical way of producing a result from one or more operands.

- What are the application operation requirements? Are those operations complex or simple? How many different operations does the application have? Do designers need a new microcontroller to execute one operation or can they use an existing one? If they use an existing one, does it execute the instruction as required in terms of clock cycle, power and speed?

- Is it more convenient to divide those operations in more simple tasks or not?

Depending on the application and design requirements this could or could not be possible. Can the microcontroller with its instruction set, execute those individual and simple tasks, or a new one is needed?

- Can those tasks be executed using more than one instruction, or is one instruction enough? The answer to this question lies on the characteristics of every microcontroller instruction and depends on the amount of tasks covered by the instruction.

## **STEP III: The Instruction Set Definition**

The instruction set should contain those instructions that the application requires. Tasks executed, amount of hardware used and clock cycles are very important parameters of an instruction. One instruction is defined as a program statement that has been changed into machine code. The CPU can understand the statement and execute it [8].

- How powerful is the instruction? The term powerful means that many tasks can be executed. This however may result in more hardware or more clock cycles per instruction.

- How many instructions are required to perform the operation? This will be determined by the power of the instruction set. The more powerful the instruction set is, fewer instructions are needed per operation.

- What kind of instructions does every microcontroller must have? Every microcontroller must have at least; logic, arithmetic, branch and data transfer instructions.

- How many complex tasks can be executed using the simplest instruction set? The basic instruction set can be combined to execute complex tasks. For example, a multiplication operation can be executed with successive execution of the addition instruction.

- What instructions should be implemented in hardware and which ones in software and why? Instructions frequently executed must be implemented in hardware. This saves programming time and size, allowing faster instruction execution. Software instructions are used depending on the application.

### **STEP IV:** The Architecture Definition

The Computer architecture refers to the basic ideas and principles in which a computer system is based on [8].

#### • The instruction operation.

The first task must always be to specify each instruction operation. After designers identify the instruction set, they must document: the instruction's name, as well as operands and execution in symbols for each one.

#### • The microcontroller bit number.

The microcontroller bit number refers to the size of the group of bits processed during instruction execution. Sometimes choosing the number of bits is as simple as analyzing the required bits for the application. In other cases there are applications in which more than certain amount of bits results unnecessary. Using more than the necessary bits may result in excessive hardware use and an increase in the circuit size, cost and power consumption.

### • The instruction format.

The instruction format specifies the order of the instruction parameters in the instruction word. Those parameters include the operational code, registers used, and additional necessary data for the instruction execution.

#### • The instruction format organization

The instruction word parameters can be organized as designers want. In this work the operational code will be at the left most side, next are the registers used during the operation and finally the additional data used for the instruction execution.

### • The Operational Code (Opcode).

The number of instructions decides the necessary bits for the operational code. The operational code identifies each instruction with a unique code for its execution.

### • Addressing modes

The addressing modes decide the amount of registers used for data processing. The addressing modes used during the instruction execution decides if more bits have to be used to address the data or not and this affects the size of the instruction word.

#### • Bits used for the Register File.

The number of registers used in the Register File determines how many address bits in the instruction word are required to address one specific location in it.

• Number of data buses.

The number of data buses in use determines the amount of data processed per clock cycle. Using more than one data bus can save clock cycles per instructions, but increases the data path and control unit circuit complexity.

- **Control Line Bus:** In this work the control lines will be connected to the control unit.

- Address Bus: Depending on design requirements the address bus is not necessary if the address bits can be transferred using the data bus. A dual role requires additional hardware.

- I/O Handling: Will the I/O ports be memory mapped or handled separately. Memory mapped ports do not require special I/O instructions.

# **STEP V:** The Arithmetic Logic Unit

In step V, the goal is to design the Arithmetic Logic Unit circuit. The ALU is the CPU component where mathematical and logical operations are executed.

#### • ALU components

The individual circuits that execute all the arithmetic and logical operations are joined together as one unit to compose the Arithmetic Logic Unit.

### • Testing

Testing is a very important task in this step. Designers must ensure that every individual circuit in the ALU correctly does every calculation.

# **STEP VI: The Register File**

A register is a small high-speed memory circuit that holds binary data [8]. In This step, the Register File is developed. The Register File is a group of registers used to store data during the instruction execution. It is an important element because data needs to be stored between clock cycles for further processing.

#### • Implementation alternatives

The number of data buses in the microcontroller determines the Register File design. Sometimes more than one data bus is used to accept and release data simultaneously in one clock cycle. Designers must decide how many data buses will be used in the microcontroller because the Register File will use the same number.

#### • The number of registers for the application

This is an important design parameter because it affects not only The Register File size but also the Instruction Register size because the IR has bits dedicated for the Register File address. Designers must select the number of necessary registers to hold data in each instruction clock cycle.

### **STEP VII: The Instruction Register (IR)**

The Instruction Register holds the instruction word that will be executed. It is designed at this stage because the numbers of instructions, registers used and the architecture have been defined. The IR is connected to the control unit, the Register File and the data path.

- **Implementation alternative:** The IR implementation consists of a register or a group of registers that holds the instruction word.

- Size: It will be easier if the size is equal to the word size because then, the instruction word holds all the required information for the instruction execution. The memory output is connected to the IR to load every single program instruction line. The IR does not have to be the same size of the data bus because it just transfers data and does not contain any other information about the instruction.

# **STEP VIII: Data Path**

The microcontroller data path is the configuration of all the circuits used for data processing. Some key points are very important in this step. It is implemented at this stage because all the necessary circuits have been designed.

#### • Layout

Designers must be creative and use strategic thinking to make the best circuit arrangement in order to achieve the instruction execution using the minimum amount of hardware and clock cycles.

### • Clock cycles

The Register File plays an important role in the number of clock cycles per instruction. More data can be processed at the same time depending on the amount of the Register File input and output ports. Also, another important element is the number of additional registers in the data path used to hold data between clock cycles. This can make a difference in the number of clock cycles per instruction if designers know how to use them.

### **STEP IX:** The PC, Jump and data transfer instructions

The instructions developed at this stage use the existing data path hardware and additional necessary circuits added in it for instruction execution.

- Those instructions need additional circuit support because some of them make decisions between clock cycles. Those circuits are used only when their instructions are executed. It is very important to test those circuits before using them for support. Another reason for using additional hardware is that more than one task per clock cycle is executed in those instructions.

- Block diagram to show the added elements. It is convenient to show the added elements to the data path to see its transformation into a more complex one.

- The Program counter. The program counter was introduced in section 5.3.1 and is developed at this step. This step presents the PC implementation and interconnection in the microcontroller circuit.

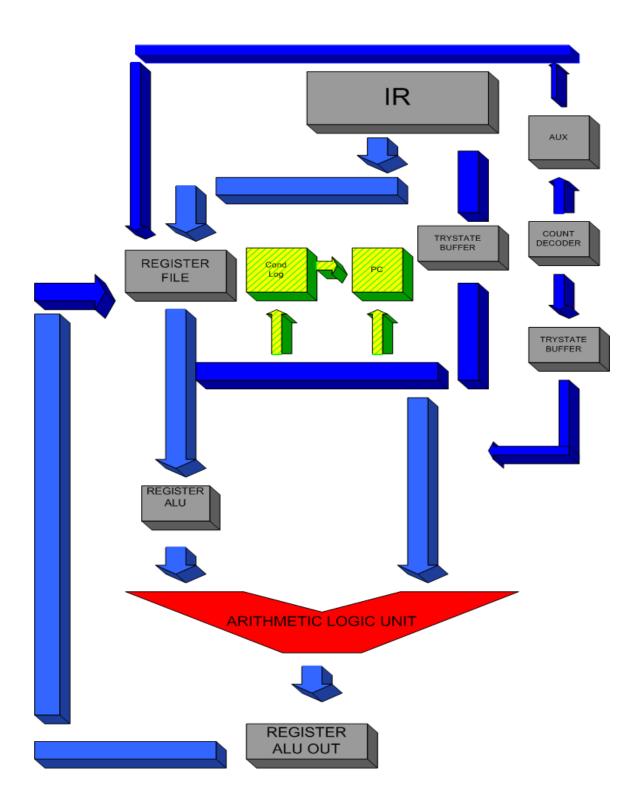

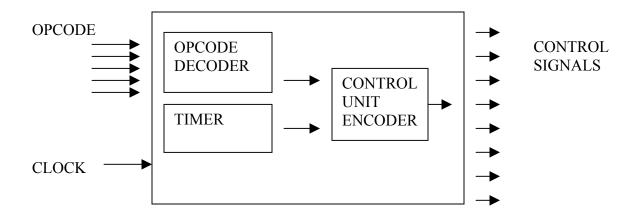

# **STEP X:** The Control Unit

The control unit is the CPU section that decodes program instructions and controls their execution. It takes control of every circuit signal in the microcontroller, activating or deactivating those signals in each clock cycle. The signal activation and deactivation per clock cycle make possible the flow of data through all data path circuits. The circuit arrangement determines the amount of processed data in each clock cycle. Then, as more data is processed per clock cycle fewer of them are needed. The developing method used in this work requires that designers "run" by hand every single instruction and take notes of which circuit signals are activated and deactivated per clock cycle.

### • Timer

The timer is a counter that goes from zero to seven and is used to specify each instruction clock cycle.

### • Operational Code Decoder

This element receives one specific instruction code and release one signal that indicates the microcontroller to execute it.

### • Control Unit Encoder

The Control Unit Encoder receives input signals from the opcode decoder and from the timer. The Control Unit Encoder activates the corresponding circuit signals that have to be active in the specified instruction in every clock cycle.

### • Implementation Alternatives

The preceding explanation of the control unit operation is implemented using logic circuits for the control unit encoder and the opcode decoder. There is another way of implementation that consists in the use of one ROM that has all the signal activation and deactivation per clock cycle. The control unit implementing this approach uses the opcode to identify the instruction location in ROM. Each line code in ROM represents each instruction clock cycle and the code in every line just controls (activates or deactivates) all the data path circuit signals.

# **Chapter 5 The Microcontroller Design Example**

# 5.1 STEP I and II The Microcontroller Justification and Operations

The purpose of this chapter is to provide the reader an example of the methodology described in chapter 4. Step I, and II will not be developed in this example because our intention is to show the design and implementation of one general-purpose microcontroller.

## **5.2 STEP III:** The Instruction Set

The choice of microcontrollers instruction set is not standardized due to designers and customers preferences. The microcontroller instructions are classified according to their operation. Table 5.1 presents the basic instruction set for the microcontroller of this work. In this table the transfer notation is used to show the instruction results. Here A  $\leftarrow$ B + C for example means that the contents of A is substituted by the result of B + C. Those instructions were selected to show the reader an example of the most common instructions used in microcontrollers.

| NAME                       | MNEMONIC | ADDRESSING<br>MODES | OPERAN<br>DS | TRANSFER<br>NOTATION            |  |  |  |  |  |  |  |  |

|----------------------------|----------|---------------------|--------------|---------------------------------|--|--|--|--|--|--|--|--|

| ARITHMETIC INSTRUCTION SET |          |                     |              |                                 |  |  |  |  |  |  |  |  |

| ADDITION                   | ADD      | Register            | B, C         | $A \leftarrow (B + C)$          |  |  |  |  |  |  |  |  |

| SUBSTRACT                  | SUB      | Register            | B, C         | $A \leftarrow (B - C)$          |  |  |  |  |  |  |  |  |

| INMEDIATE<br>ADDITION      | ADDI     | Immediate           | B, DATA      | A $\leftarrow$ (B+DATA)         |  |  |  |  |  |  |  |  |

| INMEDIATE<br>SUBSTRACTION  | SUBI     | Immediate           | B, DATA      | $A \leftarrow (B \text{-DATA})$ |  |  |  |  |  |  |  |  |

| AND                       | AND      | Register    | B, C        | $A \leftarrow (B \bullet C)$        |  |  |

|---------------------------|----------|-------------|-------------|-------------------------------------|--|--|

| OR                        | OR       | Register    | B, C        | $A \leftarrow (B(+)C)$              |  |  |

| INMEDIATE<br>AND          | ANDI     | Immediate   | B, DATA     | $A \leftarrow (B \bullet DATA)$     |  |  |

| INMEDIATE OR              | ORI      | Immediate   | B, DATA     | $A \leftarrow (B(+) DATA)$          |  |  |

| SHIFT RIGHT               | SHR      | Register    | n           | (1n) Bi+n B j+n B k+n<br>← BiBjBkBl |  |  |

| ARITHMETIC<br>SHIFT RIGHT | SHRA     | Register    | n           | (nBi) Bi+n B j+n B k+<br>← BiBjBkBl |  |  |

| CIRCULAR<br>SHIFT         | SHC      | Register    | n           | (nBl) Bi+n B j+n B k+<br>← BiBjBkBl |  |  |

| SHIFT LEFT                | SHL      | Register    | n           | Bj-n Bk-n B1-n (1n) ←<br>BiBjBkBl   |  |  |

| NOT                       | NOT      | Register    | В           | -(B) ← B                            |  |  |

| LOAD                      | LD A, M  | DATA TRANSF | A, M        | A ← M                               |  |  |

| STORE                     | STR M, A | Register    | А, М        | $M \leftarrow A$                    |  |  |

|                           |          | BRANCH      |             |                                     |  |  |