# METHODS FOR SCALABLE LEVELS OF PARALLELISM IN RADIX-2 FFTS FOR FPGA SYNTHESIS

By

Felipe Minotta Zapata

A thesis submitted in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

in

### ELECTRICAL ENGINEERING

# UNIVERSITY OF PUERTO RICO MAYAGÜEZ CAMPUS

May, 2014

Approved by:

Manuel Jiménez, Ph.D. Chairman, Graduate Committee

Gladys O. Ducoudray, Ph.D. Member, Graduate Committee

Rogelio Palomera, Ph.D. Member, Graduate Committee

Domingo Rodríguez, Ph.D. Member, Graduate Committee

Ana C. Gonzalez, M.S. Graduate Studies Representative

Pedro I. Rivera-Vega, Ph.D. Department Chairperson Date

Date

Date

Date

Date

Date

Abstract of Thesis Presented to the Graduate School of the University of Puerto Rico in Partial Fulfillment of the Requirements for the Degree of Master of Science

## METHODS FOR SCALABLE LEVELS OF PARALLELISM IN RADIX-2 FFTS FOR FPGA SYNTHESIS

By

Felipe Minotta Zapata

May 2014

Chair: Dr. Manuel Jiménez Department: Electrical and Computer Engineering Department

The Fast Fourier Transform (FFT) is the main block in many communication systems and signal processing applications, as it allows the fast computation of the discrete Fourier transform (DFT). The DFT, in turn, is used to obtain the spectrum of any finite discrete signal. Hardware implementations of this operation are highly regarded as they provide improved performance with respect to software-based implementations. The purpose of this work was developing a consistent and scalable procedure of generating the address patterns of permutation for any power-of-2 transform size and any folding factor in FFT cores with addressing schemes. Our approach was, mainly, based in  $2\beta$  memory blocks, an address generator, and  $\beta$  radix-2 butterflies. The number  $\beta$  of butterflies determines the level of parallelism. The expected high performance of this FFT core lies in the fact it does not need dedicated permutation hardware between stages. Instead, the data flow is controlled by an address generator. Using this scheme, the impact on consumed resources is significantly mitigated when the number of points of the core is increased. As a result, we obtained a fully scalable FFT core including parallelism level, number of points, and numeric format using this approach.

Resumen de tesis presentado a la Escuela Graduada de la Universidad de Puerto Rico como requisito parcial de los requerimientos para el grado de Maestría en Ciencias

# MÉTODOS PARA ESCALAR LOS NIVELES DE PARALELISMO EN FFTS DE BASE 2 PARA SÍNTESIS EN FPGA

Por

Felipe Minotta Zapata

Mayo 2014

Consejero: Dr. Manuel Jiménez Departamento: Ingeniería Eléctrica y Computadoras

La Transformada Rápida de Fourier (FFT por sus siglas en inglés) es el bloque principal en muchos sistemas de comunicación y aplicaciones de procesamiento de señales, ya que permite la rapida computación de la Transformada Discreta de Fourier (DFT por sus siglas en inglés). Por su parte, la DFT es usada para obtener el espectro de cualquier señal discreta finita. Las implementaciones en hardware de esta operación son altamente apreciadas debido a que proveen mayor rendimiento con respecto a las implementaciones basadas en software. El propósito de este trabajo fue el desarrollar un procedimiento consistente y escalable para generar los patrones de direccionamiento de las permutaciones para cualquier tamaño de transformada potencia de 2 y cualquier factor de plegado en núcleos FFT con esquemas de direccionamiento. Nuestro diseño se basó, principalmente, en  $2\beta$  bloques de memoria, un generador de direcciones y  $\beta$  mariposas base 2. El número  $\beta$  de mariposas determina el nivel de paralelismo. El alto rendimiento del núcleo radica en el hecho de que el flujo de datos es controlado por un generador de direcciones, el cual mitiga el consumo de recursos cuando se incrementa el número de puntos de la FFT. Como resultado, se obtuvo una implementación de FFT enteramente escalable incluyendo el nivel de paralelismo, número de puntos y formato numérico usando este enfoque.

To my family, specially to my mother Patricia, my father Francisco, and little sis Maria José, who have always given me their love, affection and support to keep going.

# Acknowledgements

I would like to express my thanks to my advisor Professor Dr. Manuel Jiménez, thank you for encouraging my research and for allowing me to grow as a student, researcher, and professional. Also, thanks to my committee members, professor Dr. Domingo Rodríguez, professor Dr. Rogelio Palomera, professor Dr. Gladys O. Ducodray, for serving as my committee and for taking part in the review of my work. I would especially like to thank Sandy, the graduate academic counselor and friend, who guided and helped me through this experience in a new university and country. Last but not least, I want to thanks all my Puerto Rican and Colombian friends, who have encourage and supported me to move forward during good and bad moments.

# Table of Contents

| Abs            | tract  | in English                                                                                         |

|----------------|--------|----------------------------------------------------------------------------------------------------|

| $\mathbf{Abs}$ | tract  | in Spanish                                                                                         |

| Ded            | licate | d to                                                                                               |

| Ack            | nowl   | $edgements \qquad \dots \qquad \dots \qquad \dots \qquad \dots \qquad \dots \qquad \dots \qquad v$ |

| List           | of T   | ables                                                                                              |

| List           | of F   | igures                                                                                             |

| 1              | INT    | RODUCTION                                                                                          |

| 2              | TH     | EORETICAL BACKGROUND                                                                               |

|                | 2.1    | Discrete Fourier Transform (DFT)                                                                   |

|                | 2.2    | The Fast Fourier Transform (FFT)                                                                   |

|                | 2.3    | Pease FFT Factorization                                                                            |

| 3              | PRI    | EVIOUS WORK                                                                                        |

|                | 3.1    | FFTs with address generation                                                                       |

|                | 3.2    | FFTs with dedicated data permutation logic                                                         |

|                | 3.3    | Summary                                                                                            |

| 4              | PRO    | DBLEM STATEMENT AND HYPOTHESIS                                                                     |

|                | 4.1    | Problem Statement                                                                                  |

|                | 4.2    | Hypothesis                                                                                         |

| 5              | OBJ    | ECTIVES                                                                                            |

|                | 5.1    | General Objective                                                                                  |

|                | 5.2    | Specific Objectives                                                                                |

| 6              | ME'    | <b>THODOLOGY</b>                                                                                   |

|                | 6.1    | System Blocks and FFT Architecture                                                                 |

|     | 6.2    | Number Representation Format        |

|-----|--------|-------------------------------------|

|     | 6.3    | Arithmetic Unit Design              |

|     |        | 6.3.1 Complex Adder/Subtractor      |

|     |        | 6.3.2 Complex Multiplier            |

|     | 6.4    | Memory Organization                 |

|     | 6.5    | Data Switch Design                  |

|     |        | 6.5.1 Data Switch (Read)            |

|     |        | 6.5.2 Data Switch (Write)           |

|     | 6.6    | Address Generation Schemes          |

|     |        | 6.6.1 Data Address Generator Design |

|     |        | 6.6.2 Phase Factor Scheduler Design |

| 7   | RES    | ULTS AND ANALYSIS                   |

|     | 7.1    | Core Validation                     |

|     | 7.2    | Timing Performance                  |

|     | 7.3    | Resource Consumption                |

|     | 7.4    | Analysis and Comparisons            |

|     | 7.5    | Limitations                         |

| 8   | CON    | VCLUSIONS                           |

| 9   | CON    | NTRIBUTIONS AND FUTURE WORK         |

| Bib | liogra | phy                                 |

# List of Tables

# List of Figures

| 2.1                                                        | Graphical representation of the operation in Eqs. 2.10 and 2.11 $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2.2                                                        | Bit<br>reversal and stride-2 permutations example for $N=8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                  |

| 2.3                                                        | 8-point Pease FFT Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                  |

| 2.4                                                        | 8-point Pease FFT with horizontal folding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                  |

| 6.1                                                        | Basic Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                 |

| 6.2<br>(c)                                                 | (a) Single Precision Floating Point (b) Double Precision Floating Point<br>) Quadruple Precision Floating Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                                                                                 |

| 6.3                                                        | Radix-2 Butterfly Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                                                                 |

| 6.4                                                        | Complex Adder Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                                 |

| 6.5                                                        | Complex Multiplier Architecture 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                                                 |

| 6.6                                                        | Complex Multiplier Architecture 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                                 |

| 6.7                                                        | Memory Access Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                                 |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

| 6.8<br>sti                                                 | (a) Bit Reversal Permutation. (b) Stride-2 Permutation. (c) Modified ride-2 Permutation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                                                 |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27<br>28                                                                           |

| sti                                                        | ride-2 Permutation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

| stı<br>6.9                                                 | ride-2 Permutation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28                                                                                 |

| str<br>6.9<br>6.10                                         | ride-2 Permutation.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 28<br>28                                                                           |

| str<br>6.9<br>6.10<br>6.11                                 | ride-2 Permutation.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 28<br>28<br>29                                                                     |

| str<br>6.9<br>6.10<br>6.11<br>6.12                         | ride-2 Permutation.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 28<br>28<br>29<br>29                                                               |

| str<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13                 | ride-2 Permutation.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 28<br>28<br>29<br>29<br>30                                                         |

| str<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14         | ride-2 PermutationData Switch (Read).Bit-reversal Permutation.Stride-2 Permutation.Modified Stride-2 Permutation.(a) First Permutation(b) Second Permutation<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28<br>28<br>29<br>29<br>30<br>30                                                   |

| str<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br>6.15 | ride-2 PermutationData Switch (Read).Bit-reversal Permutation.Stride-2 Permutation.Modified Stride-2 Permutation.(a) First Permutation(b) Second PermutationData Switch (Write).Data Addressing Sequence with $N = 16$ and $\beta = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ol> <li>28</li> <li>29</li> <li>29</li> <li>30</li> <li>30</li> <li>32</li> </ol> |

| 6.19 | How Modified Stride-2 Permutation is calculated throughout the stages           | 36 |

|------|---------------------------------------------------------------------------------|----|

| 6.20 | Phase Factor Scheduling for $N = 32$ and $\beta = 1$                            | 37 |

| 6.21 | Phase Factor Scheduling for $N = 32$ and $\beta = 2$                            | 37 |

| 6.22 | Phase Factor Scheduling for $N = 32$ and $\beta = 4$                            | 38 |

| 6.23 | Principal parameters behaviour of the phase factor scheduling for $N = 32$      | 38 |

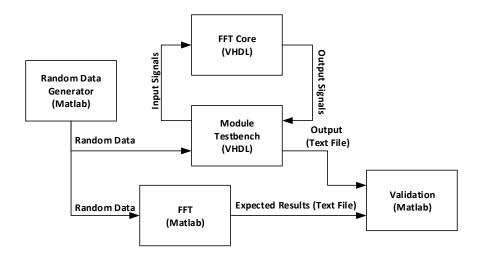

| 7.1  | Structure used to validate the simulation of the FFT $\ldots$ $\ldots$ $\ldots$ | 41 |

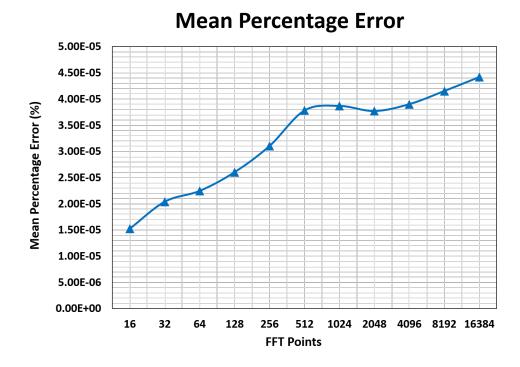

| 7.2  | Mean Percentage Error of our core compared with MATLAB                          | 42 |

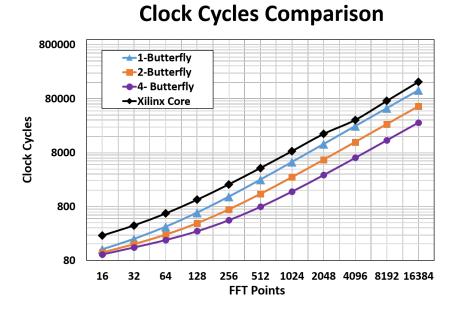

| 7.3  | Clock Cycles Comparison                                                         | 43 |

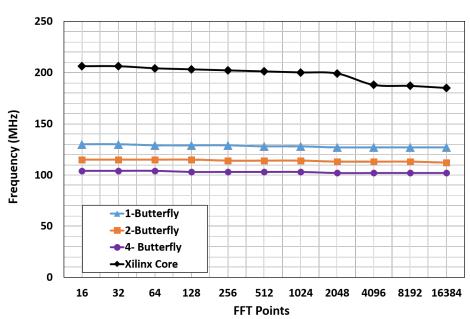

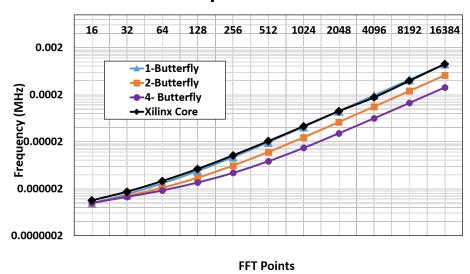

| 7.4  | Maximum Working Frequency Comparison                                            | 43 |

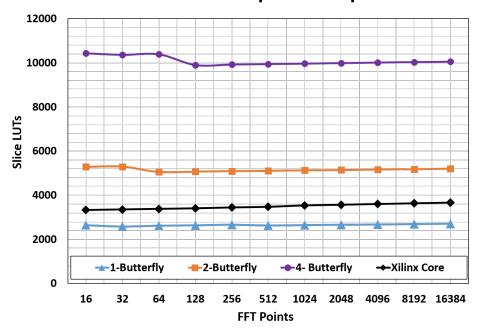

| 7.5  | Slice LUTs Consumption Comparison                                               | 44 |

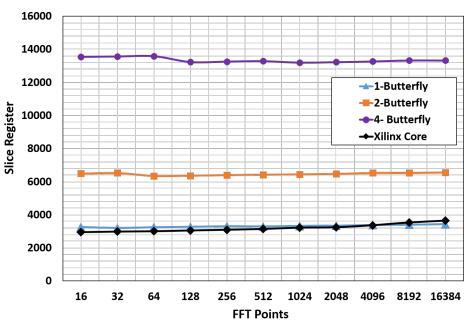

| 7.6  | Slice Register Consumption Comparison                                           | 45 |

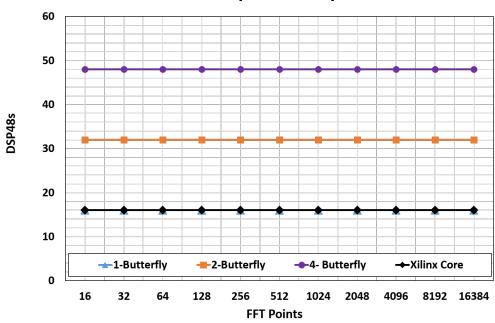

| 7.7  | DSP48 Consumption Comparison                                                    | 45 |

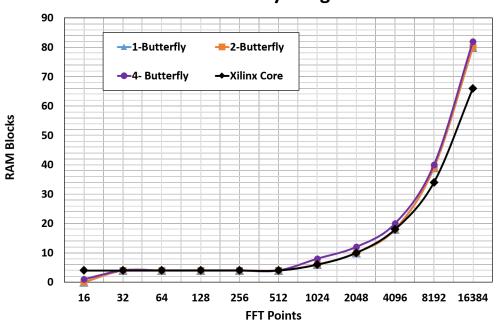

| 7.8  | Memory Usage Comparison                                                         | 46 |

| 7.9  | Computation Time                                                                | 48 |

# Chapter 1 INTRODUCTION

The Fast Fourier Transform (FFT) is a fundamental tool in signal processing and communication systems to obtain the frequency of signals. Hardware implementations of the FFT are highly regarded as they provide improved performance characteristic with respect to software-based sequential implementations. Developing an efficient hardware implementation represents a significant burden for hardware engineers today despite feel that an FFT algorithm can be easily understood.

A typical FFT core is composed of processing elements and a resulting permutation blocks. The processing elements are arithmetic blocks and the number of them is defined by the folding factor  $\phi$ , which determine the level of parallelism in the implementation. The permutation block can be implemented with dedicated logic or with an addressing scheme. This document presents a method to design the permutation block when the folding factor is scaled in FFT cores implemented on FPGA using an address generation scheme. Our effort was centered in the development of a general addressing scheme that could perform the necessary permutations through the stages regardless the number of points and folding factor.

The following Chapter presents the theoretical foundations of this work. Chapter 3 presents a considerable number of hardware implementations of FFTs. Problem Statement and Objectives of this thesis are shown in Chapters 4 and 5 respectively. Chapter 6 shows complete design in hardware of our FFT core, and the outcome of our design including performance and consumed resources are presented in Chapter 7. Finally, we present the contributions and the future work in the remaining Chapter.

# Chapter 2 THEORETICAL BACKGROUND

This chapter presents the underlying concepts behind our work. In the first part, we review the original Discrete Fourier Transform (DFT) formulation. Then, we explain the Fast Fourier Transform (FFT) Cooley-Tukey formulation [1] and its advantages. Afterwards, we explain why we chose the Pease factorization of the FFT. And, how we can modify the Pease architecture to obtain a trade-off between latency and hardware consumed resources. Finally, we explain why one would choose addressing generation schemes over dedicated permutation logic.

### 2.1 Discrete Fourier Transform (DFT)

The DFT is an operator that takes a finite-length sequence, representing a signal in the time domain, and transforms the signal to the frequency domain. The DFT of an arbitrary discrete signal x[n], of length N, is given by

$$X[k] = \sum_{n=0}^{N-1} x[n] e^{-j2\pi \frac{kn}{N}} \quad 0 \le k \le N-1,$$

(2.1)

where X[k] is the signal in the frequency domain. Commonly, the DFT definition is also expressed by making the substitution

$$W_N = e^{-j2\pi\frac{kn}{N}},\tag{2.2}$$

where the  $W_N$  values are commonly named phase or twiddle factors. This substitution allows us to represent the DFT as a matrix multiplication of the form:

$$\mathbf{X} = \mathbf{W}_N \times \mathbf{x} \tag{2.3}$$

where  $\mathbf{x}$  is a column vector representing the signal in the time domain,  $\mathbf{X}$  is a column vector representing the signal in the frequency domain, and  $\mathbf{W}_N$  is a square matrix whose elements are given by Equation 2.2. Thus, we can represent:

$$\mathbf{X} = \begin{bmatrix} X[0] \\ X[1] \\ X[2] \\ \dots \\ X[N-1] \end{bmatrix} \quad \mathbf{x} = \begin{bmatrix} x[0] \\ x[1] \\ x[2] \\ \dots \\ x[N-1] \end{bmatrix} \quad (2.4)$$

$$\mathbf{W}_{N} = \frac{1}{\sqrt{N}} \begin{bmatrix} 1 & 1 & 1 & \dots & 1 \\ 1 & W_{N} & W_{N}^{2} & \dots & W_{N}^{N-1} \\ 1 & W_{N}^{2} & W_{N}^{4} & \dots & W_{N}^{2(N-1)} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ 1 & W_{N}^{N-1} & W_{N}^{2(N-1)} & \dots & W^{(N-1)(N-1)} \end{bmatrix} \quad (2.5)$$

#### 2.2 The Fast Fourier Transform (FFT)

The algorithm for the DFT is considered computationally expensive as it requires  $O(N^2)$  operations. The development of the FFT algorithm by Cooley-Tukey in 1965 simplified the practical implementation of the DFT as it reduced the number of operations to  $O(N \log_2 N)$  [1]. The FFT formulations are based on the periodicity and symmetry properties of the Twiddle Factors, i.e. the elements of  $W_N$  in Equation 2.5, and the fact that an FFT of N points can be expressed as 2 FFTs of  $\frac{N}{2}$  points. The linearity property allows for expressing the DFT as two different summations, one with the indexed even values and the other with indexed odd values, as shown in equation 2.6 and 2.7.

$$X[k] = \frac{1}{\sqrt{N}} \sum_{r=0}^{N/2-1} x[2r] W_N^{2rk} + \frac{1}{\sqrt{N}} \sum_{r=0}^{N/2-1} x[2r+1] W_N^{(2r+1)k}$$

(2.6)

$$X[k] = \frac{1}{\sqrt{N}} \sum_{r=0}^{N/2-1} x[2r](W_N^2)^{rk} + W_N^k \frac{1}{\sqrt{N}} \sum_{r=0}^{N/2-1} x[2r+1](W_N^2)^{rk}$$

(2.7)

Due to the symmetry in  $W_N$ , we have that  $W_N^2 = exp(-j\frac{4\pi}{N}) = W_{N/2}$ . Therefore, both summations correspond to two independent DFT implementations, the first one with the indexed even input values and second one with the indexed odd input values, as shown in Equation 2.8.

$$X[k] = \frac{1}{\sqrt{N}} \sum_{r=0}^{N/2-1} x[2r] W_{N/2}^{rk} + W_N^k \frac{1}{\sqrt{N}} \sum_{r=0}^{N/2-1} x[2r+1] W_{N/2}^{rk}$$

(2.8)

According to the Equation 2.8, it can be observed that the term  $W_N^k$  affecting the second DFT corresponds to a shift in the time domain in one sample. Which was expected, since the difference between a odd sample and a even sample is one. Finally, Equation 2.8 can be rewritten as,

$$X[k] = F[k] + W_N^k G[k], (2.9)$$

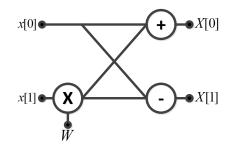

where F[k] and G[k] are the DFT of the even indexed and odd indexed samples of signal x[n] respectively. Equation 2.9 suggests that the calculation of an N-point FFT can be made making successive 2-points FFT partitions of the original input signal. Each 2-point FFT is simple as it is only composed of a multiplication, an addition, and a subtraction (Equation 2.10 and Equation 2.11) and is called a butterfly due to its graphical representation (Figure 2.1). It only takes to combine the solution of all 2-point FFTs for several stages to obtain the complete FFT

$$X[0] = x[0] + W * x[1]$$

(2.10)

$$X[1] = x[0] - W * x[1]$$

(2.11)

Figure 2.1 : Graphical representation of the operation in Eqs. 2.10 and 2.11

#### 2.3 Pease FFT Factorization

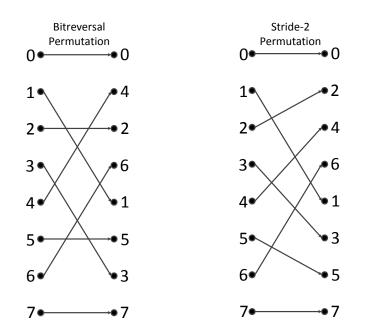

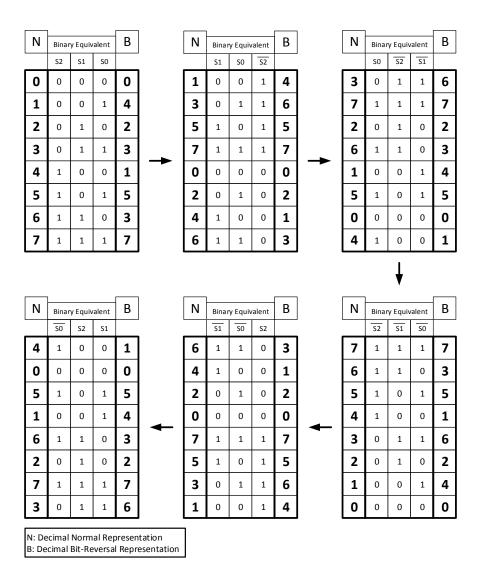

After Cooley-Tukey [1], Pease [2], Korn and Lambiotte [3], and Stockham [4] performed different factorizations to the original formulation of the FFT. The Pease factorization is one of the most suitable for our purposes due to its repeating structure. For the development of the Pease algorithm, only two permutations are needed. Figure 2.2 shows how the permutations are performed for N = 8. The first permutation is a bit-reversal and is only performed at the beginning of the algorithm. This permutation can be thought of as doing a mirror operation on the  $\log_2(N)$ -bit word representing the index of every value of the signal. The second permutation is called a Stride-2 permutation which is performed in the rest of the algorithm. A Stride-2 permutation separates the signal values into two groups one with even indexed values and the other with odd indexed values.

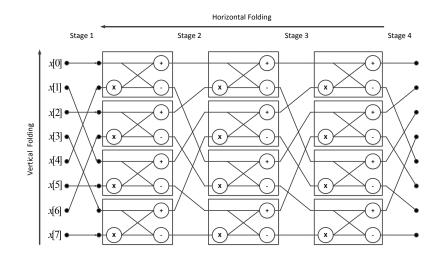

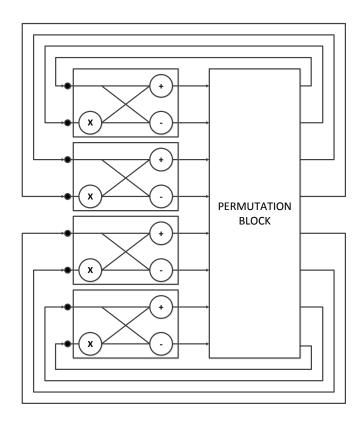

Figure 2.3 shows the structure of an 8-point Pease FFT. The rectangles contain operating elements forming the *Butterflies*. Figure 2.3 also shows the possibility of doing a horizontal and/or vertical foldings. A horizontal folding consists on reducing the number of columns, while a vertical folding applies the same process to the rows. If the original structure were implemented, the latency of the core would be  $Tb \log_2(N)$ , where Tb is the latency of a single butterfly. If we do a complete horizontal folding, we would have one column of butterflies and we would need a block to perform the permutations, as shown in the Figure 2.4. The permutation block controls the data

Figure 2.2 : Bitreversal and stride-2 permutations example for N = 8

flow between the stages. A structure with these characteristics would have a latency also depending on the number of points N and the vertical folding factor  $\phi$ . This factor consists in using one column of  $\beta$  ( $\beta = N/(2\phi)$ ) butterflies depending of the level of parallelism desired for the design. Because each butterfly accepts two points at the same time, the maximum number of  $\beta$  is N/2. This approach leads to an increase in latency but uses less arithmetic hardware resources. For this reason, a typical FFT core is implemented with a full horizontal folding and the vertical folding factor is scaled depending on the desired parallelism level. This is very important because it has a direct impact in the total latency and the consumed resources. For small values of  $\beta$ , the latency is high and the consumed resources are low. On the contrary, for large values of  $\beta$ , the latency is lower and the consumed resources are higher.

To conclude the explanation, the permutation block is implemented using dedicated permutation logic or through emulation with an addressing scheme. The former uses logic blocks to permute the data, which consumes a significant amount

Figure 2.3 : 8-point Pease FFT Architecture

of hardware resources for numerous points, while the latter indirectly performs the permutations by addressing the data from multi-bank memories. This represents an enhancement in design automation and implementation. Previous works using the addressing scheme, which are presented in the Chapter 3, have shown that this is a resource-efficient implementation, which is why our work is based on this approach.

Figure 2.4 : 8-point Pease FFT with horizontal folding

# Chapter 3 PREVIOUS WORK

In this Chapter, a relevant hardware implementations of FFT documented in recent literature are discussed. The approaches reviewed here can be classified in two groups: FFT designs based on address generation schemes and dedicated permutation logic. In the first group, data are stored in memories and a block generates the addresses depending the permutation needed. In the second group, there is a dedicated logic to control the data flow. In this Chapter, we make a review of the works considered more relevant in this kind of approaches.

Section 3.1 summarizes the characteristics for address generation FFTs, followed in Section 3.2 by a discussion of different dedicated permutation logic FFTs. The Chapter concludes with a summary of the most important characteristics of the discussed methods.

#### 3.1 FFTs with address generation

Johnson described an address generation scheme for decimation in time and decimation in frequency for radix r FFTs [5]. The author explains how to generate addresses using shifters and address for both data and phase factors. The method uses multi-bank memories, such that all data needed at a given butterfly could be accessed at once. It uses conflict-free addressing by writing into the same locations being read. The proposed addressing allowed to keep the data storage requirement at N locations. This is a theoretical work, with no hardware implementation. From

the point of view of consumed resources, this design was suitable for large values of N.

Wang, et al, designed and implemented a 64-point FFT to meet the requirements of Wireless Local Area Network (WLAN) [6]. The design was based on the radix-2 decimation in frequency algorithm. The hardware required for complex multiplication at the butterfly was reduced using a convenient factorization that allowed for using only three real multipliers. The author uses a conflict-free memory addressing scheme for minimum memory requirements. The design also took advantage of the property of reusability of the phase factors so it only required storage for 11 of them. The design was not scalable and the complete FFT calculation could be completed after 76 clock cycles at a maximum frequency of 31.69 MHz on an Altera's Cyclone II device.

Polychronakis, et al, presented a parallel addressing technique for radix-2 decimation in frequency FFT architectures [7]. The processor used a single memory with N/2 location, which stored two FFT elements at each address. Address generation was specified to access data throughout the stages. However, there is no documentation of how the twiddle factors were generated, and the numeric format used. An example of a 256-point FFT with 12 bits real part and 12 bits imaginary were provided. The entire processor occupied 213 slices and 6 of 48 DSP48Es of a Xilinx Virtex XC5VLX50T-3.

Gautam, et al, designed and implemented a scalable radix-2 FFT core for OFDM applications [8]. The processor used conflict free in-place memory for intermediate data storage. The address generator was scalable to support up to 2<sup>13</sup> points. The twiddle factors were generated using CORDIC (CO-ordinate Rotational Digital Computer). An 8-point FFT was implemented on a Xilinx Virtex-5 FPGA "xc5vlx100t-3-ff1136". The authors reported a 200 MHz as a maximum allowed frequency for this core.

Hongxia and Shitan presented an addressing scheme for twiddle factors in an FFT with mixed-radix based on multi-bank memory [9]. The memory for twiddles were improved using the quarter of the locations due to reusability. The design was based on a look-up table to stores the twiddle factors by a maximum value of N and the address generator was capable of addressing for values less than or equal of N. However, since the lookup table is the same for any number of points, implementations with a low number of points has a large memory consumption.

Chad, et al, presented a design method for a real-time decimation in frequency radix-4 1024 point FFT processor [10]. The processor worked in fixed point and used an overflow controller which controls dynamically shift of fix point operand according to the result of the butterfly. The author also showed a method of address mapping and generation with in-place memory addressing strategy. The twiddle factors were generated and the complex multiplications for this operation were implemented using a lifting scheme that allowed for using three real multipliers. The system was capable of completing a radix-4 butterfly per clock cycle. The maximum supported frequency was 127 MHz and execution time of  $10.1\mu$ .

Szedo, et al, proposed a 16-bit, 1024-point, radix-4 decimation in frequency, radix-4 FFT core [11]. The system used two butterflies, the first one for the first  $\log_4(N) - 1$  ranks and a second one multiplication free for the last rank. The core used 4 memory banks of four dual port block memories and took exactly 1024 clock cycles to process data continuously. The maximum frequency was 100 MHz and consumed 2593 logic slices, 12 multipliers and 22 block RAMs.

Ramesh, et al, evaluated the use of address generation algorithms for accelerating the execution of DSP Kernels [12]. In their article they showed the implementation of address generation units for accessing data in bit reversed order for FFTs and in zig-zag order for Discrete Cosine Transform (DCT). To illustrate the algorithm, the authors gave an example in which they implemented an 8-point FFT and the address generation unit for twiddle factors was also developed. They completed the 8-point FFT in 28 cycles. The address generation scheme produced a single data address at a time. Using the proposed scheme they claimed to complete a N-point FFT in  $N \log_2 N$  cycles.

Jiang, et al, designed a radix-2 FFT algorithm to reduce the frequency of memory accessed as well as multiplication operations [13]. This achievement was made by reusing the phase factor during the calculation of the transform. The reduction of the frequency of memory accessed was achieved using temporal registers to store the twiddle factors while they are needed. The reduction of the multiplication operations was accomplished taking advantage of several twiddle factors that are equal to 1. With the proposed approach, the required memory accesses due to phase factors was reduced to N/2 - 1.

Tsai, et al, proposed an address generation scheme for multiple processing units [14]. It specified an addressing scheme for data values but it did not account for twiddles addressing. Fixed and mixed radix operations were possible. The method completed calculations in  $N/2 \log_8 N$  cycles and required 2N data locations for a size N transform. The work did not describe any implementation on FPGA or ASIC.

Xiao, et al, proposed a method for designing the address generator with reduced logic [15]. The address generator avoids the parity checkers an barrel shifters and is primarily based on inverters, counters, and multiplexors. The system used the minimum memory requirements for in-place operation. As case study they synthesized a 16-point FFT with 32 bit complex number using CMOS  $0.18\mu m$  technology. For a 65536-point FFT the maximum frequency supported by the address generator was 629 MHz.

Polo, et al, designed a scalable fixed point FFT core for FPGA synthesis [16]. Their approach exploited the structural regularity from the Kronecker formulation to perform a complete folding of the transform. Algorithms for producing the address sequences and phase factor scheduling were provided. The core was compared with the one developed by Xilinx and the results show an improvement of nearly 40% in slices, 6% in memory used, and 7% in latency.

Shome, et al, proposed an architectural design for a highly programmable radix-2 Decimation-in-Frequency FFT processor [17]. The design supported FFT sizes from 64 to 1024 points. The system used 5 different dual-port memories. The data were stored in the first memory. The second and third memories were used for the calculation of the FFT, and the fourth and fifth ones were used for the final data reordering. The system described were only an Address Generation Block for the data and phase factor. No results about consumed hardware resources and latency were reported.

Yang, et al, implemented a memory based radix-2 Decimation-in-frequency FFT processor with address generation [18]. The architecture used 4 single port memories instead of two dual-port memories. The system performed an N-point FFT in  $\log_2 N+1$  clock cycles. The twiddle factors were stored in a ROM but the addressing scheme were not specified.

Wey, et al, proposed a radix-2 memory-based FFT design suitable for OFDM applications which used an address generator approach to perform data permutation [19]. The architecture used single port instead dual port memories for area saving. The design achieved reduced resource consumption and required storage for N data words using 24 bit width in fixed point. However, no address generation scheme was specified for phase factors and they were stored in a ROM. The design was synthesized to an ASIC and had a maximum operating frequency of 198 MHz and a latency of 55296 cycles for a 8192-point FFT.

Frias, et al, developed a 1024-point decimation in time radix4 FFT VHDL core [20]. The developed core was implemented on a Xilinx Spartan-3 XC3S200 FPGA by taking advantage of the FPGAs low cost. The FFT calculation was reported to run in 7680 cycles with a 50MHz master clock. The processor worked in fixed point. The computation time was  $153.84\mu$ s. Although it had lower performance than commercially available cores from Xilinx, it had the advantage of using fewer on-chip resources, making it feasible to be implemented in lower cost FPGAs like Spartan-3.

Ayinala, et al, developed a scalable architecture for in-place Fast Fourier Transform computation for real valued signals [21]. The proposed computation was based on a modified radix-2 algorithm, which removed the redundant operations from the flow graph. The architecture used two radix-2 butterflies to process four inputs in parallel. Address generation was specified to access data throughout the stages but there was no explanation of how the twiddle factors were generated. In the article, they showed the latency for different number of points but they did not specify the numeric format. The address generation was extended to support multiple processing elements and it had 12 different addressing patterns depending on the stage.

### 3.2 FFTs with dedicated data permutation logic

Babionitakis, et al, presented an implementation of a 4096-point radix-4 complex FFT on a Virtex II FPGA and a VLSI chip [22]. The input values of the architecture were expressed in fixed point. The maximum frequency was 200MHz and the throughput was of  $4096/20.48\mu$ s for the FPGA. The VLSI implementation achieved a throughput of  $4096/3.89\mu$ s and a worst case post-route frequency of 604.5MHz using a  $0.13\mu$ m process.

Yang, et al, proposed an FFT processor suitable for MIMO-OFDM based SDR systems [23]. Synthesized using a  $0.13\mu$ m standard cell library, the design supported 64, 128, 512, 1024 and 2048 point transform lengths. The processor used mixed radix algorithms which minimized the number of non-trivial multiplications. The core supported computation of the transform on four channels simultaneously. The design improved over a previous 4-channel radix-2 multiple delay commutator based

design both in memory and logic resource consumption, achieving 16.4% and 26.8% reduction respectively.

Montaño, et al, designed an scalable floating point FFT core for Xilinxs FPGAs [24]. The scalable parameters included size, word length and folding factor. The data permutations were made using an array of switches. This permutation hardware did not allow for sizes beyond 64 points when targeting a Xilinx Virtex IV device. Phase factors scheduling had no re-use, thus requiring full tabulation and logic resources for their storage instead of a ROM.

Chen, et al, proposed a permutation network for configurable and scalable FFT processors [25]. It consisted of several independent RAM blocks and two interconnection networks, capable of operating in a pipeline fashion. The authors claimed their method achieved a high level of parallelism, thus high throughput, for sizes ranging from 2 to 8192 points, obtained by implementing various computational stages and permutation networks together. The reported results regarding the performance and logic consumption were not clear since the authors did not specify under which parameters, procedures and technology the numbers were obtained.

#### 3.3 Summary

Table 3.1 summarizes the works reviewed and their relevant aspects. None of the reviewed works address an architecture with scalable folding factor which is the main scope of this proposal. It can be seen that only one work deals with floating point, twelve with fixed point, and five others do not specify number format. Our approach is expected to work with any numeric format.

| Author            | Number Format  | Scalable   | Address Generation | Radix |

|-------------------|----------------|------------|--------------------|-------|

| Wang [6]          | Fixed Point    | No (64p)   | $\Box \Delta$      | 2     |

| Polychronakis [7] | Fixed Point    | No (256p)  |                    | 2     |

| Gautam [8]        | Fixed Point    | Yes        |                    | 2     |

| Hongxia [9]       | N/S            | Yes        | Δ                  | Mixed |

| Chad [10]         | Fixed Point    | No (1024p) |                    | 4     |

| Szedo [11]        | Fixed Point    | No (1024p) |                    | 4     |

| Ramesh [12]       | Fixed Point    | Yes        |                    | 2     |

| Jiang [13]        | N/S            | Yes        |                    | 2     |

| Tsai [14]         | N/S            | Yes        | $\Box \Delta$      | $2^q$ |

| Xiao [15]         | Fixed Point    | Yes        |                    | 2     |

| Polo [16]         | Fixed Point    | Yes        |                    | 2     |

| Shome [17]        | N/S            | Yes        | $\Box \Delta$      | 2     |

| Yang [18]         | N/S            | Yes        | $\Box \Delta$      | 2     |

| Wey [19]          | Fixed Point    | Yes        |                    | 2     |

| Frias [20]        | Fixed Point    | No (1024p) |                    | 4     |

| Ayinala [21]      | N/S            | No         |                    | 2     |

| Babionitakis [22] | Fixed Point    | No (4096p) | No                 | 4     |

| Yang [23]         | Fixed Point    | Yes        | No                 | 2     |

| Montaño [24]      | Floating Point | Yes        | No                 | 2     |

| Chen [25]         | N/S            | Yes        | None               | 2     |

|                   | 1              | 1          | 1                  | 1     |

Table 3.1 : Summary of reviewed works

Legend:  $\Box$ :Data Address Generation  $\triangle$ :Twiddle Address Generation

# Chapter 4 PROBLEM STATEMENT AND HYPOTHESIS

## 4.1 Problem Statement

The problem addressed in this thesis is that of generating the address patterns of permutations when the folding factor is scaled in FFT cores. To the best of our knowledge, although there have been implementations for specific folding factors, no generalized approaches have been reported. This generalized addressing mode allows scaling the level of parallelism in a FFT processor, which directly impacts the latency of the synthesized cores.

### 4.2 Hypothesis

Our work was proposed under the hypothesis that it is possible to develop a general rule of addressing regardless the folding factor of the structure. Furthermore, with this addressing, the latency is expected to decrease up to 2 times for every parallelism level without impacting significantly the consumed hardware resources.

# Chapter 5 OBJECTIVES

This section describes the objectives that have been formulated for the proposed work.

## 5.1 General Objective

To develop a method to design the permutation block when the folding factor is scaled in FFT cores based on an address generation scheme for FPGA implementation.

## 5.2 Specific Objectives

- 1. Determining which FFT algorithm offers best regularity for the general addressing for the data flow and the phase factors.

- 2. Identifying a general rule governing the pattern of the address sequence for data point and phase factor regardless the folding factor.

- 3. Designing and implementing an HDL model to test the functionality of the addressing sequence.

- 4. Analysing how architectural changes affect the latency and the hardware consumed in the HDL model when the folding factor is scaled.

# Chapter 6 METHODOLOGY

An FFT core might be designed for low latency or low hardware resources consumed depending on the application. The two types of design objectives can be achieved augmenting the level of parallelism for low latency, or reducing the level for low hardware resources consumed. The methodology established in this work is based on developing a scalable addressing scheme for both, data reordering and phase factor scheduling. In order to succeed in this task, it is necessary to develop a general addressing rule that can perform the two permutations through the stages regardless the number of points and folding factor.

In this Chapter, we first give a brief introduction to the general architecture of our core, including the main purpose of each block. In the latter sections, we explain in detail the basic functioning of each block and the respective hardware implementation.

#### 6.1 System Blocks and FFT Architecture

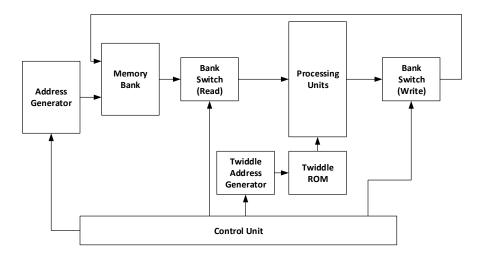

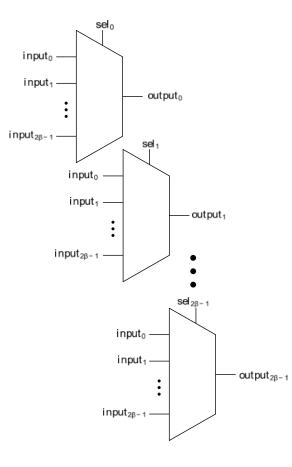

As we explained in Chapter 2, the core is composed, mainly, of an arithmetic unit and and permutation block. The former can be one or more butterflies depending the folding factor. And the latter has a memory bank, a data addresser, and data switches. Other blocks equally important are the phase factor scheduler and the control unit. This approach can be classified as Radix-2 because it is based on a Radix-2 butterflies. Also can be classified as a Burst I/O design as the user must wait for the complete FFT calculation to finish before providing a new input signal. Figure 6.1 shows the basic architecture of the core. The address generator is in charge of generating the addressing patterns to the memory bank, which is the data to be processed. The twiddle addresser generator produces the addressing patterns to the Twiddle memory in order to provide the correct phase factor to each butterfly. The read and write switches permutate the data while they are being read and written. The processing units perform the arithmetic operations over the data to be processed. Finally, the control unit generates the control signal to every block to ensure a correct functioning.

Figure 6.1 : Basic Architecture

#### 6.2 Number Representation Format

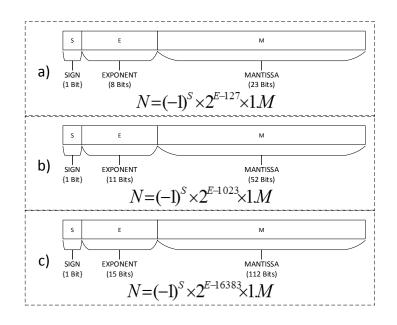

Our core is entirely based on Floating Point Arithmetic. The main advantage of Floating Point arithmetic over fixed point is the dynamic range for accommodating extremely large numbers and high precision for very small numbers. This helps to alleviate the underflow and overflow problems often seen in fixed-point formats [26]. Furthermore, this numeric format has constant bit-word size, which helps the implementation. Floating point uses a sign-magnitude representation, where the magnitude is obtained by the multiplication of a fractional and an exponential term. The IEEE-754 is the most commonly used standard for Floating Point representation. In theory, our core supports any floating point format, only limited by the FPGA resources. Figure 6.2 shows an example of the quantities we can represent in our core. Figure 6.2 a. shows a single precision floating point representation, the standard specify 8 bits for the exponent and 23 bits for the mantissa. Figure 6.2 b. shows a double precision floating point representation, which uses 11 bits for the exponent and 52 bits for the fractional part. Figure 6.2 b. shows a quadruple precision floating point representation, which offers results more reliably and accurately by minimising overflow and round-off errors in intermediate calculations since it uses 15 bits for the exponent and 112 bits for the mantissa.

Figure 6.2 : (a) Single Precision Floating Point (b) Double Precision Floating Point (c) Quadruple Precision Floating Point

#### 6.3 Arithmetic Unit Design

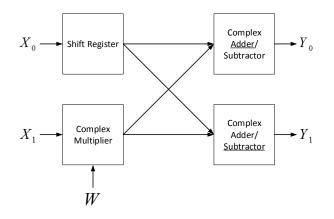

As explained earlier, the FFT calculation is performed around a basic arithmetic unit called a Butterfly. This unit consists of a complex adder/subtractor, and a complex multiplier. For the hardware implementation, floating point was used to represent the numbers. Every unit was optimized to work is this numeric format. Due to the complexity of the involved operations, the most efficient architecture to implement the Butterfly is a pipeline architecture. The resulting butterfly had an initial non-zero latency of 20 cycles, after which it was capable of producing a pair of outputs per clock cycle. Figure 6.3 shows the architecture of the complex radix-2 butterfly.

Figure 6.3 : Radix-2 Butterfly Structure

#### 6.3.1 Complex Adder/Subtractor

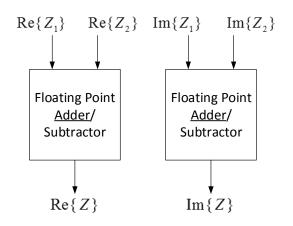

The addition/substraction of any two complex numbers  $Z_1$ ,  $Z_2$ , where  $Z_1 = X_1 + jY_1$  and  $Z_2 = X_2 + jY_2$ , is performed as indicated by Equation 6.1. Thus a Complex Adder/Subtractor requires two floating point adders, the first to add the real part and the second to operate the imaginary part.

$$Z = Z_1 + Z_2 = (X_1 + X_2) + j(Y_1 + Y_2)$$

(6.1)

Figure 6.4 shows the diagram of a complex adder. Also, in the Figure it can be seen that the latency of the complex adder is the same as the floating point adder, in our case to five cycles.

Figure 6.4 : Complex Adder Architecture

#### 6.3.2 Complex Multiplier

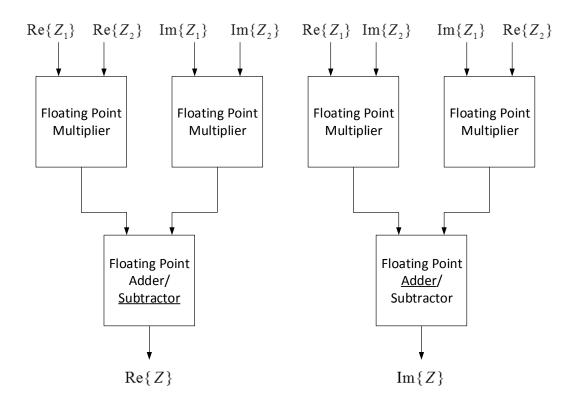

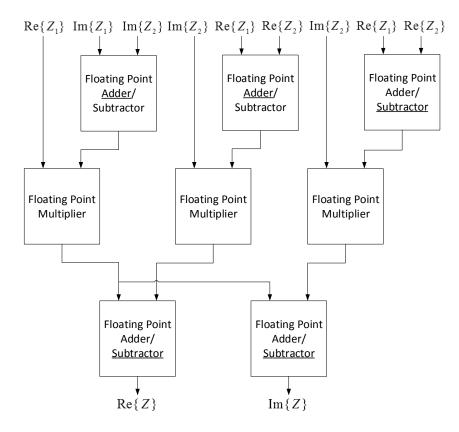

The multiplication of any two complex numbers  $Z_1$ ,  $Z_2$ , where  $Z_1 = X_1 + jY_1$ and  $Z_2 = X_2 + jY_2$ , can be performed as indicated by Equations 6.2 and 6.3.

$$Z = (X_{1} + jY_{1}) \times (X_{2} + jY_{2})$$

$$\operatorname{Re}\{Z\} = X_{1} \times (X_{2} + Y_{2}) - Y_{2} \times (X_{1} + Y_{1})$$

$$\operatorname{Im}\{Z\} = X_{1} \times (X_{2} + Y_{2}) - X_{2} \times (X_{1} - Y_{1})$$

$$\operatorname{Re}\{Z\} = X_{1} \times X_{2} - Y_{1} \times Y_{2}$$

$$\operatorname{Im}\{Z\} = X_{1} \times Y_{2} + Y_{1} \times X_{2}$$

(6.3)

The result shown in Equation 6.2 requires three multipliers and five adders. And the result shown in Equation 6.3 requires four multipliers and two adders. Figure 6.5 and 6.6 show the two different architectures. Since our floating point adder consumes approximately twice more resources and has the half of the latency of the multiplier, we chose the first architecture because the second consumes 13/8 times more resources and it spends 5 cycles less than the first one.

Figure 6.5 : Complex Multiplier Architecture 1

### 6.4 Memory Organization

Two different memory units were needed in this implementation. The first stores the signal in the time domain, the intermediate data during calculation, and the signal in the frequency domain. The second stores the phase factors.

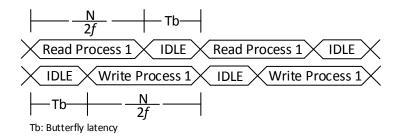

Since every butterfly needed two different values at the same time, the data memory in our design consisted of a bank of  $2\beta$  memory blocks. For simplicity, the signal in the time domain was first stored in the same order it was produced. Since our implementation was intended to use an "in place" strategy [5], every memory had  $N/(2\beta)$  locations. The memory access process using this strategy consisted on first fetching the data, processing them, and then writing them into the same locations. This process is depicted in Figure 6.7. Since the write and read operation may

Figure 6.6 : Complex Multiplier Architecture 2

overlap, every memory unit had two different address ports to allow for this operations to be performed simultaneously.

Figure 6.7 : Memory Access Process

The phase factor memory size is different depending on the folding factor. As every butterfly needs a different phase factor, when the structure is completely folded, a single port memory is used. When the structure is not completely folded, a dualport memory is used to minimize the memory usage. Regarding to the memory usage, we took advantage of the periodicity and symmetry properties of the phase factor. Therefore, only N/4 numbers were stored instead of N/2 as an FFT implementation normally requires [16]. Hence, the phase factor required for a FFT of N points was,

$$W_N = e^{-2\pi jk/N} \quad 0 \le k \le N/4 - 1, \tag{6.4}$$

and the other N/4 number needed were obtained using Equation 6.5

$$W_N^{k+N/4} = \operatorname{Im}\{W_N^k\} - j\operatorname{Re}\{W_N^k\}$$

(6.5)

#### 6.5 Data Switch Design

The main task of the data switches was to route the data between the memories and the arithmetic units. The data address generator is in charge of generating the correct addresses, but the data is not always in the order required by the arithmetic units. The Read Switch reorders the data as required by the arithmetic units. The Write Switch reorders the data in such a way that all the points to be fetched in the next stage be in different memories.

#### 6.5.1 Data Switch (Read)

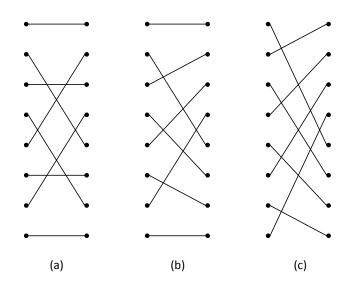

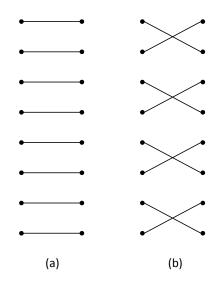

The Read Data Switch is located between the memory bank and the butterflies. This block partly contributed to performing the permutation between the stages, specifically, when data were being read. The behaviour described here is consistent for any folding factor. Figure 6.8 shows the three different permutations to be performed during calculation when four butterflies are used. Figure 6.8 a. shows the one which is performed in the first stage and is called a bit reversal permutation. Figure 6.8 b. and c show the ones which are performed in the rest of the stages in the first and second half, respectively. These are called stride-2 and modified stride-2 permutation, respectively.

Figure 6.8 : (a) Bit Reversal Permutation. (b) Stride-2 Permutation. (c) Modified stride-2 Permutation.

In hardware, this switch is implemented as an array of multiplexers like that shown in Figure 6.9. As can be seen in the Figure, this block has  $2\beta - 1$  data inputs and outputs, allowing to make any permutation over the data.

To perform the permutations, every multiplexer must choose the correct input. The three different sequences are generated with bitwise operations over a normal ordered sequence, like circular shifting and simple logical operations. Figures 6.10, 6.11 , and 6.12 show how to perform the Bit-reversal permutation, Stride-2 Permutation, and Modified Stride-2 Permutation, respectively. A bit-reversal sequence is obtained reversing the binary representation of a normally ordered sequence. A Stride-2 permutation is obtained making a left circular shifting in one position. And a Modified Stride-2 Permutation is obtained making a left circular shift by one position too, but negating the least significant bit.

Figure 6.9 : Data Switch (Read)

| Input             | Output            |

|-------------------|-------------------|

| S2 S1 S0<br>0 0 0 | S0 S1 S2<br>0 0 0 |

| 0 0 1             | 1 0 0             |

| 0 1 0             | 0 1 0             |

| 0 1 1             | 1 1 0             |

| 1 0 0             | 0 0 1             |

| 1 0 1             | 1 0 1             |

| 1 1 0             | 0 1 1             |

| 1 1 1             | 1 1 1             |

Figure 6.10 : Bit-reversal Permutation

### 6.5.2 Data Switch (Write)

The Write Data Switch is the one located between the butterflies and the memory bank. This block also partially contributes to performing of the permutation between

| Input             | Output            |

|-------------------|-------------------|

| S2 S1 S0<br>0 0 0 | S1 S0 S2<br>0 0 0 |

| 0 0 1             | 0 1 0             |

| 0 1 0             | 1 0 0             |

| 0 1 1             | 1 1 0             |

| 1 0 0             | 0 0 1             |

| 1 0 1             | 0 1 1             |

| 1 1 0             | 1 0 1             |

| 1 1 1             | 1 1 1             |

Figure 6.11 : Stride-2 Permutation

| Input<br>S2 S1 S0<br>0 0 0 | S1 S0 S2 | Output<br>S1 S0 S2 |

|----------------------------|----------|--------------------|

| 0 0 1                      | 0 1 0    | 0 1 1              |

| 0 1 0                      | 1 0 0    | 1 0 1              |

| 0 1 1                      | 1 1 0    | 1 1 1              |

| 1 0 0                      | 0 0 1    | 0 0 0              |

| 1 0 1                      | 0 1 1    | 0 1 0              |

| 1 1 0                      | 1 0 1    | 1 0 0              |

| 1 1 1                      | 1 1 1    | 1 1 0              |

Figure 6.12 : Modified Stride-2 Permutation

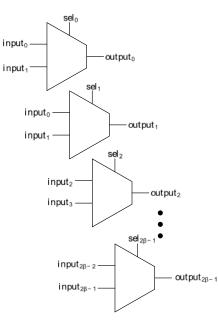

stages, specifically, when data are being written. Figure 6.13 shows the two different permutations that need to be performed during the calculation. Figure 6.13 a. shows the one performed on the even indexed butterflies of every stage. Figure 6.13 b shows the one which is performed in the odd indexed butterflies of every stage.

Since every output can have only two values, it is no necessary to include all input values in the multiplexers, just 2. Figure 6.14 shows the basic architecture of this Data Switch.

#### 6.6 Address Generation Schemes

A scalable folding of a Pease structure requires two major considerations: the ability of folding the data permutation completely or partially and the ability of

Figure 6.13 : (a) First Permutation. (b) Second Permutation.

Figure 6.14 : Data Switch (Write)

producing the correct phase factor schedule at each stage. These task were performed by two address generators which are explained next.

#### 6.6.1 Data Address Generator Design

The Data Address Generator is one of the most important blocks in this work and is the one that has the highest complexity. First at all, this block had to perform Bit-reversal permutation in the first stage and Stride-2 permutation in the next stages. Also, the design had to be scalable to support different sizes and any folding factor. Furthermore, these permutations had to be performed assuring the minimum requirements of memory. The only way to guarantee this requirement was by writing into the same locations being read.

Since  $2\beta$  memories were needed, the same number of simultaneous addresses had to be generated. Nonetheless, for any folding factor there were only two different sequences. Therefore, the hardware implementation only required two different address generator blocks.

In the work developed by Polo, et al, the first access and the data arrangement depended on the number of butterflies [16]. For example, with one 1 butterfly, the data in the two memories had to be arranged in stride-2 organization and the data was accessed in normal order. With two butterflies, the data in the four memories had to be arranged in stride-4 organization and the data was accessed in normal order. To introduce regularity to the system, we proposed to arrange the data in normal order in all cases and the first access to each memory made it in bit-reversal order. Thus, the first permutation needed was performed automatically and the first access was always the same.

Figures 6.15 to 6.17 show the addressing sequences for different numbers of butterflies and transform sizes. These sequences were obtained running a core emulation in MATLAB. By analysing these sequences, it can be seen that the addressing of the even indexed memories are obtained making a Stride-2 Permutation of the previous sequence and of the odd indexed memories are obtained making a modified Stride-2 Permutation of the previous sequence. This addressing sequence applied for any number of butterflies and any power-of-2 transform size. Following the last statements, we can formally express mathematically the address patterns, that is, for an N-point FFT with vertical folding factor  $\phi$  the addressing sequences can be expressed as:

$$X_{i+1} = L_2^{2\frac{\phi}{2}} X_i \quad X_0 = R_{2^{\log_2(\phi)}} \begin{bmatrix} 0\\1\\2\\\vdots\\\phi-1 \end{bmatrix} \quad 0 \le i \le \log_2(N) - 1 \quad (6.6)$$